Digital Logic Basics Review - Sequential Logic

Summary

TLDRThis video provides a comprehensive introduction to sequential logic, focusing on latches, flip-flops, and finite state machines. It explains the operation of D-latches and edge-triggered flip-flops, highlighting their role in memory storage during clock cycles. The presentation delves into the mechanics of these components, emphasizing the timing diagrams and the significance of clock edges in data transfer. Additionally, it illustrates the concept of a finite state machine through a practical example of a railway crossing control system, demonstrating how states transition based on inputs and clock signals, ultimately reinforcing the principles of digital logic design.

Takeaways

- 😀 Sequential logic, also known as time domain logic, utilizes memory elements such as latches and flip-flops for data storage.

- 🔄 The D-latch allows the output (Q) to track the input (D) while the clock signal is high and stores the value when the clock goes low.

- ⏰ Edge-triggered flip-flops sample the input at the rising edge of the clock, ensuring data is stored correctly.

- 🔗 A master-slave flip-flop consists of two latches, where the first tracks the input while the clock is low, and the second transfers the value to the output when the clock is high.

- 🛑 Flip-flops help create parallelism in digital circuits by allowing simultaneous operations across multiple flip-flops during each clock cycle.

- 📊 The behavior of combinational logic between clock edges influences the output of flip-flops, which retain their values until the next clock edge.

- 🚦 Finite State Machines (FSMs) are used to control systems with defined states, such as traffic signals at a railway crossing.

- 🔄 State transitions in an FSM occur on clock edges, allowing for predictable behavior based on input changes.

- ⚙️ Logic gates calculate the next state and output based on current states and inputs, enabling the design of complex digital circuits.

- 🔍 The timing diagrams illustrate how states and outputs change over clock cycles, providing a clear representation of the system's behavior.

Q & A

What is the primary function of latches and flip-flops in sequential logic?

-Latches and flip-flops serve as memory components that store data in sequential logic, allowing for the retention of information based on clock signals.

How does a D-latch operate?

-A D-latch has an input D, an output Q, and a clock signal. When the clock is high, Q tracks D; when the clock goes low, Q stores the last value of D.

What is the difference between a latch and an edge-triggered flip-flop?

-A latch is level-sensitive, meaning it changes its output based on the input while the clock is high, whereas an edge-triggered flip-flop changes its output only on the rising or falling edge of the clock.

Can you explain the master-slave flip-flop configuration?

-In a master-slave flip-flop, the first latch (master) tracks the input while the clock is low, and the second latch (slave) stores the master latch's output when the clock is high, ensuring a stable output until the next clock edge.

What role does combinational logic play between clock edges in a sequential circuit?

-Combinational logic processes the outputs of flip-flops between clock edges, evaluating inputs and generating new outputs based on the current stored values, but these new outputs are not stored until the next clock edge.

How does a finite state machine (FSM) function?

-A finite state machine transitions between a defined set of states based on input signals, with each state producing specific outputs controlled by a clock signal.

In the railway crossing example, what are the two states of the FSM?

-The two states of the FSM in the railway crossing example are 'Go' (where the red light is off) and 'Stop' (where the red light is on).

What is the significance of clock edges in the operation of sequential circuits?

-Clock edges trigger transitions in flip-flops and FSMs, ensuring that state changes and data storage occur at specific intervals, which is crucial for the synchronized operation of digital circuits.

Why is it important to have a reset mechanism in a finite state machine?

-A reset mechanism is important to ensure that the FSM starts in a known state, allowing it to function correctly and consistently in response to input signals.

How does parallelism in digital logic enhance circuit performance?

-Parallelism allows multiple flip-flops to operate simultaneously across a circuit, enabling faster data processing and reducing the time required for state transitions in complex digital systems.

Outlines

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantMindmap

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantKeywords

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantHighlights

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantTranscripts

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantVoir Plus de Vidéos Connexes

Part 5.2 #Latches and #FlipFlops #SequentialCircuits in Digital Electronics in Hindi

Latch and Flip-Flop Explained | Difference between the Latch and Flip-Flop

FLIP-FLOP - Jenis dan tabel kebenaran

Digital Electronics (DE) All 5 Units Important Questions AKTU BOE310/BOE410 & BEE401 B.Tech 2nd Year

O QUE É O FLIP FLOP? | Como Funcionam os Flip Flops JK, SR, D e T | Eletrônica Digital

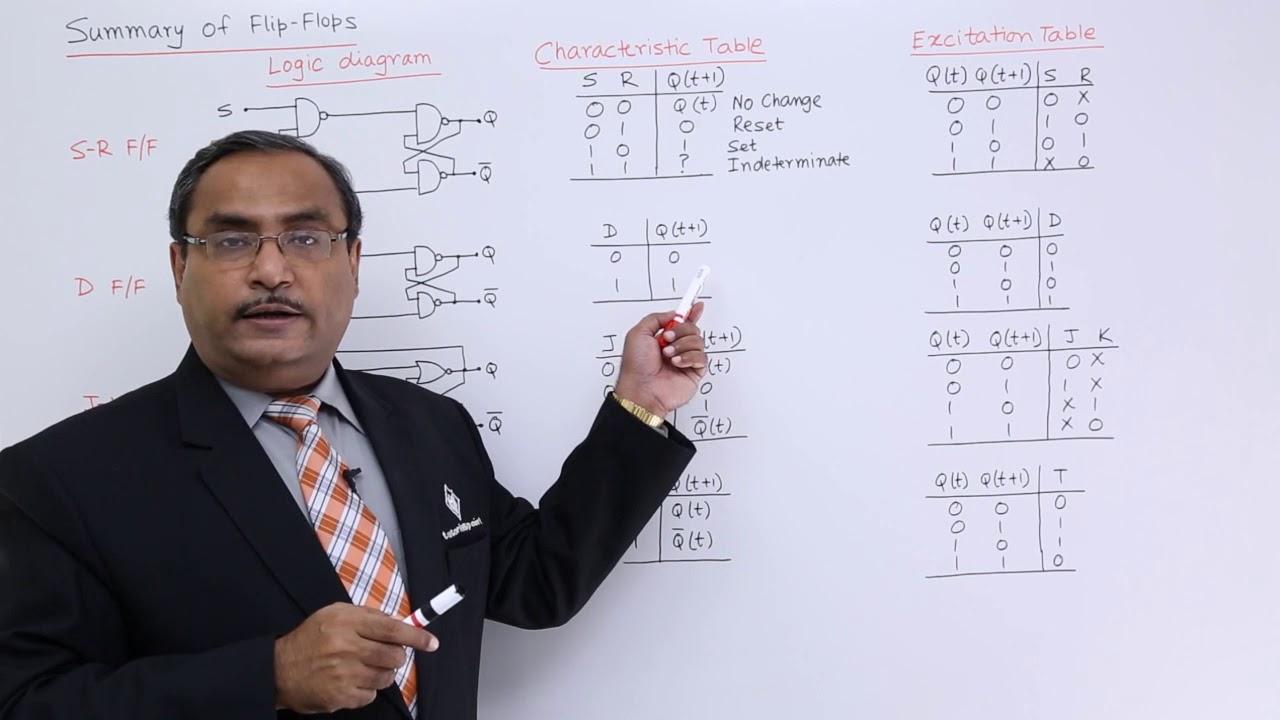

Summary of all Flip-Flops

5.0 / 5 (0 votes)