Latches and Flip-Flops 6 - The JK Flip Flop

Summary

TLDRThe video script delves into the versatility of the JK flip-flop, a fundamental building block in digital electronics used in various applications like shift registers and counters. It contrasts the JK flip-flop with the SR latch, highlighting the JK's ability to avoid unpredictable behavior with invalid input combinations. The script explains the construction of JK latches from both NOR and NAND gates and their transition to flip-flops with the introduction of an enabling input and clock signal. It also demonstrates how the JK flip-flop operates as a toggle device when J and K inputs are combined.

Takeaways

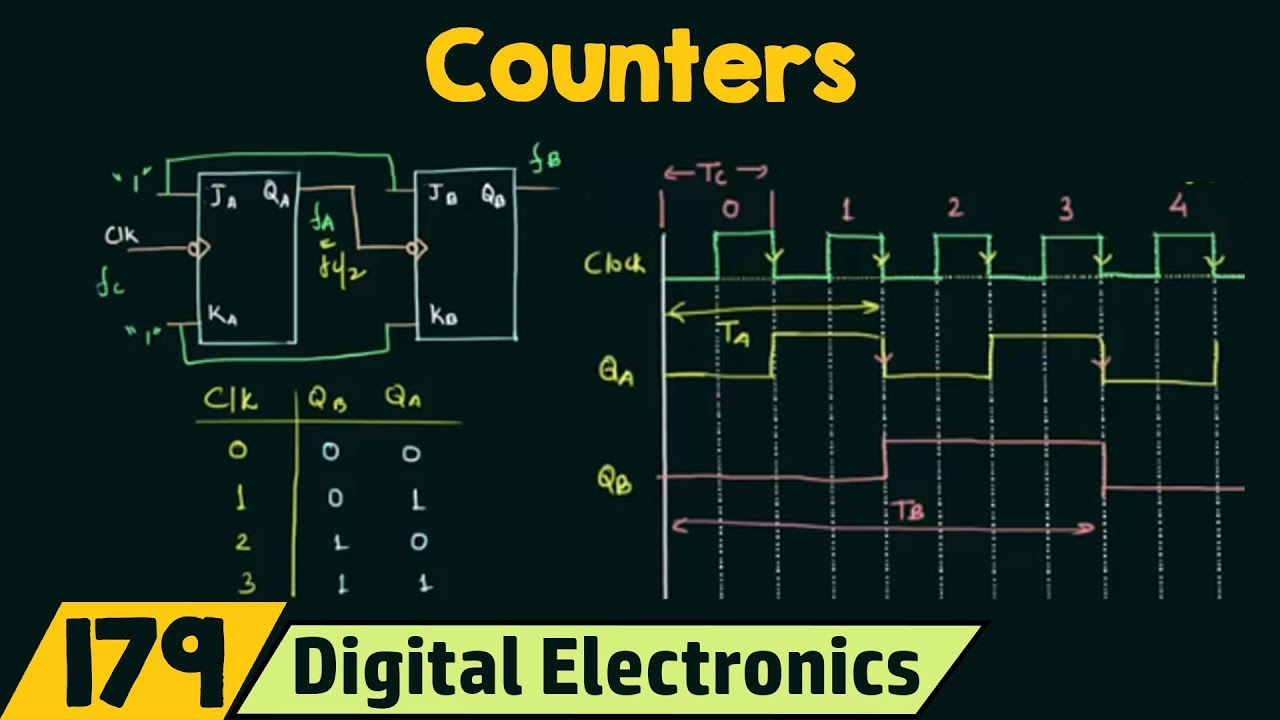

- 🔄 The JK flip-flop is a versatile component used in various applications such as shift registers, ripple counters, event detectors, and frequency dividers.

- 🌐 It is known as the universal programmable flip-flop because it can mimic the behavior of other flip-flop types by manipulating its inputs.

- 🚫 The JK flip-flop overcomes the limitation of the set-reset latch, which can exhibit unpredictable behavior with certain input combinations.

- 🔩 The set-reset latch built from NOR gates has an active-high configuration, while the one built from NAND gates is active-low.

- 🔄 In a set-reset latch, an invalid input combination of both S and R being high can lead to a race condition and unpredictable output states.

- 🔄 The JK latch, a precursor to the JK flip-flop, can be built from both NOR and NAND gates, eliminating the invalid state issue of the set-reset latch.

- 🔄 A JK latch built from NOR gates will oscillate between states when both J and K inputs are high, while a NAND-based JK latch behaves similarly.

- 🔒 Adding an enabling input (E) to the JK latch allows it to respond to J and K inputs only when E is high, effectively gating the latch.

- ⏲️ The JK flip-flop operates on the rising edge of a clock signal, toggling its state when both J and K are high during this transition.

- 📊 A modified truth table can describe the behavior of the JK flip-flop, showing how Q changes on the rising edge of the clock based on J and K inputs.

- 🔄 By connecting J and K together and labeling it as 'T' for toggle, the JK flip-flop can be adapted to create a T flip-flop that toggles state on the rising edge of the clock when T is high.

Q & A

What is a JK flip-flop and why is it considered versatile?

-A JK flip-flop is a type of bistable multivibrator that can be used as a shift register, ripple counter, event detector, frequency divider, and more. It is considered versatile because it can be manipulated to behave like other types of flip-flops, overcoming limitations of set-reset latches.

What is the main advantage of a JK flip-flop over a set-reset latch?

-The main advantage of a JK flip-flop over a set-reset latch is that it eliminates the issue of unpredictable behavior when both set and reset inputs are high simultaneously, which is an invalid state for a set-reset latch.

How does an SR latch built from NOR gates work?

-An SR latch built from NOR gates operates with active high inputs. The output Q is set to 1 when a high pulse is applied at S, and reset to 0 when a high pulse is applied at R. The latch holds the last value when both inputs are low.

What is the problem with an SR latch when both S and R inputs are high?

-When both S and R inputs of an SR latch are high, it creates an invalid state where the latch is told to store both 1 and 0 at the same time. This results in Q and not Q both becoming 0, leading to unpredictable behavior.

How does an SR latch built from NAND gates differ from one built from NOR gates?

-An SR latch built from NAND gates is active low, meaning S and R should be kept high and a low pulse at either S or R will set or reset the latch, respectively. It avoids the same invalid state issue as the NOR-based latch when both inputs are high.

What is a JK latch and how does it differ from a JK flip-flop?

-A JK latch is a modified version of an SR latch with added AND gates at the inputs, labeled J and K for set and reset. It differs from a JK flip-flop in that it does not have a clock signal and can oscillate between states when both J and K are high.

How does a JK flip-flop solve the invalid inputs problem of an SR latch?

-A JK flip-flop solves the invalid inputs problem by using AND gates at the inputs, which ensures that when both J and K are high, the flip-flop toggles between states rather than resulting in an invalid state.

What is the purpose of the enabling input 'E' in a gated JK latch?

-The enabling input 'E' in a gated JK latch is used to control when the latch responds to the J and K inputs. The latch only updates its state when 'E' is high and the clock signal is on the rising edge.

How can a JK flip-flop be adapted to create a toggle flip-flop?

-A JK flip-flop can be adapted to create a toggle flip-flop by connecting J and K together to form a single toggle input. This results in the flip-flop changing state only when the toggle input is high during the rising edge of the clock signal.

What is the significance of the rising edge detector in a JK flip-flop?

-The rising edge detector in a JK flip-flop ensures that the flip-flop only reacts to the inputs during the rising edge of the clock pulse. This prevents the flip-flop from oscillating uncontrollably when J and K are both high.

How is the toggling behavior of a JK flip-flop described in its truth table?

-The toggling behavior of a JK flip-flop is described in its modified truth table, where a rising edge of the clock pulse causes the output Q to change to its opposite state when both J and K are high, while leaving Q unchanged otherwise.

Outlines

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantMindmap

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantKeywords

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantHighlights

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantTranscripts

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantVoir Plus de Vidéos Connexes

Master Slave JK Flip Flop | Digital Electronics

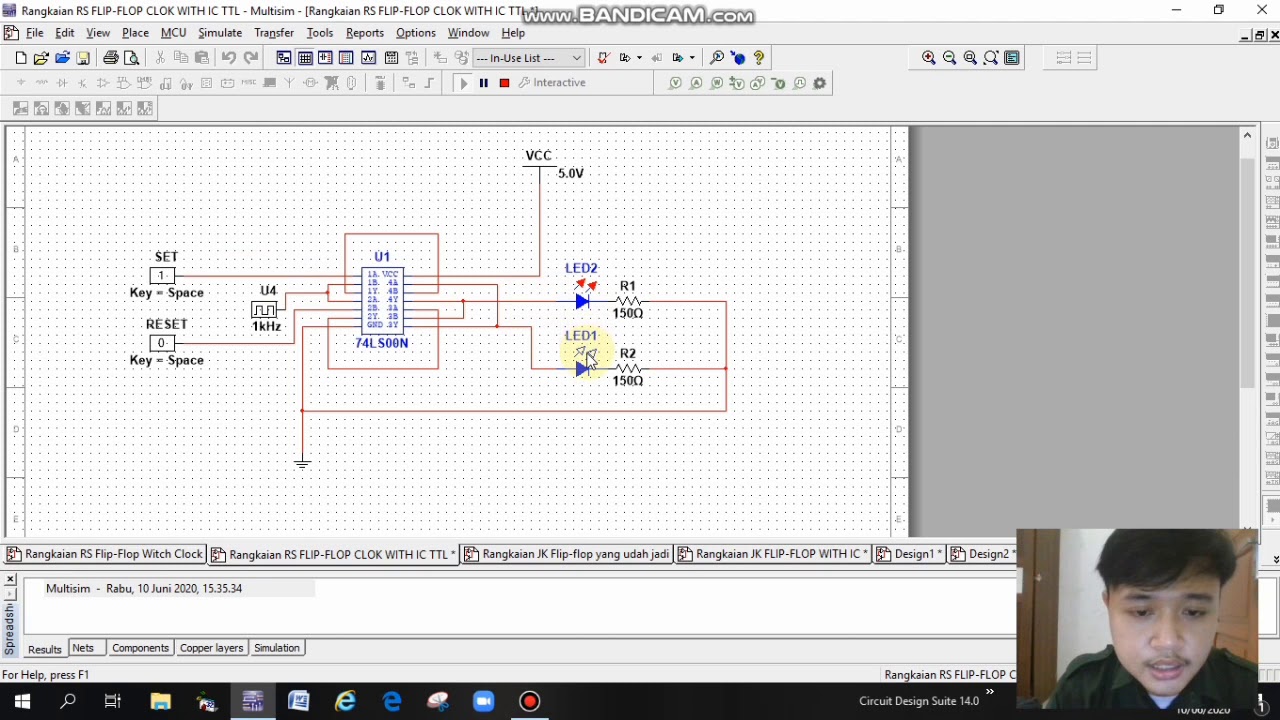

Simulasi Rangkaian JK Flip-flop, RS Flip-flop, dan D Flip-flop ( Faishal Satria G 2211181006 )

Dasar Sistem Digital | 09 - Register & Counter

FLIP-FLOP - Jenis dan tabel kebenaran

Introduction to Counters | Important

Introduction to Sequential Circuits | Important

5.0 / 5 (0 votes)