Introduction to Counters | Important

Summary

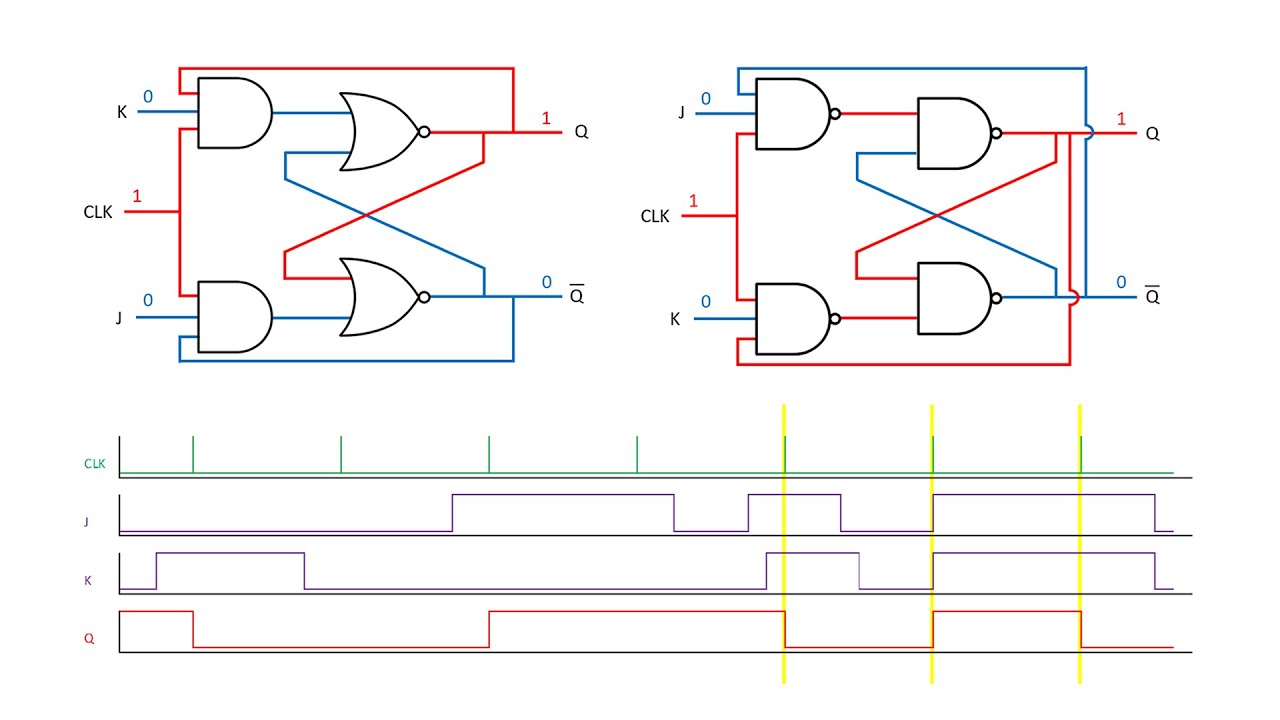

TLDRThis video explains the working of digital counters using JK flip-flops, focusing on their role in frequency division. By toggling the output at each clock pulse, JK flip-flops divide the clock frequency, and by cascading multiple flip-flops, the counter can count up to a desired value. The video demonstrates a simple counter that counts from 0 to 3, and extends this to larger counters, explaining how the number of flip-flops determines the range of the counter. The video provides key insights into the design and operation of counters, offering valuable understanding for students and enthusiasts of digital electronics.

Takeaways

- 😀 A counter is a sequential circuit that increments its state with each clock pulse, with the start and end numbers determined by the design.

- 😀 Counters can be designed to count within specific ranges, such as 0-10, 2-6, or 3-9, based on the required application.

- 😀 JK flip-flops are used in counters to divide the frequency of the clock signal, where each flip-flop halves the frequency of the previous stage.

- 😀 A divide-by-2 circuit can be built using two JK flip-flops, where the clock pulse triggers a frequency division by a factor of 2 with each additional flip-flop.

- 😀 The output frequency (FA) of the first flip-flop is FC/2, and the second flip-flop's output frequency (FB) is FC/4, where FC is the input clock frequency.

- 😀 The frequency division by multiple flip-flops follows the formula: Frequency after P flip-flops = FC / 2^P.

- 😀 For a two-flip-flop counter, the frequency is divided by 4 (2^2), and for a four-flip-flop counter, it is divided by 16 (2^4).

- 😀 Each flip-flop in the counter toggles its state on the falling edge of the clock, which ensures sequential counting without race conditions.

- 😀 The counter's output is a binary representation of the number of clock pulses that have passed. For example, QA = 0, QB = 0 for 0 pulses, and QA = 1, QB = 1 for 3 pulses.

- 😀 The counter's cycle starts over once it reaches the maximum count (e.g., 3 for a 2-bit counter or 15 for a 4-bit counter), allowing for continuous counting.

- 😀 By extending the counter with more flip-flops, the maximum count range increases exponentially, with each flip-flop doubling the count range.

- 😀 Understanding the relationship between the time period of the flip-flop output and the clock frequency is crucial to correctly calculating and interpreting the counter's behavior.

Q & A

What is a counter in digital electronics?

-A counter is a sequential circuit that counts in a specific sequence. It increments from a starting value to an ending value, depending on the design. For example, it could count from 0 to 10, or from 3 to 9.

What is the role of a JK flip-flop in a counter circuit?

-In a counter circuit, a JK flip-flop is used to toggle between two states (0 and 1). It helps to divide the frequency of the input clock signal, enabling the counter to track the number of clock pulses.

Why is the JK flip-flop considered a divide-by-2 circuit in this context?

-The JK flip-flop in this setup is considered a divide-by-2 circuit because it divides the frequency of the clock signal by 2. When the clock pulse is fed to the first flip-flop, the output frequency of that flip-flop (QA) is half the frequency of the input clock (FC).

What does it mean for a flip-flop to be 'negative edge-triggered'?

-A negative edge-triggered flip-flop changes its state only on the falling edge of the clock signal (when the clock goes from high to low). This helps avoid issues like race conditions and ensures stable operation.

How does the frequency change from the first flip-flop to the second flip-flop in the circuit?

-The frequency of the second flip-flop (QB) is half the frequency of the first flip-flop (QA). Since the first flip-flop divides the clock frequency by 2, the second flip-flop divides that frequency again by 2, resulting in a frequency of FC/4 for the second flip-flop.

How do the outputs QA and QB relate to the counting process in this circuit?

-The outputs QA and QB represent the state of the counter. By analyzing these outputs, you can determine how many clock pulses have occurred. The counter counts in binary, where each unique combination of QA and QB represents a different count.

How does the counter in this circuit count from 0 to 3?

-The counter uses two flip-flops. For each clock pulse, the values of QA and QB change, allowing the counter to progress through the binary states: 00 (0), 01 (1), 10 (2), and 11 (3). After the fourth clock pulse, it resets to 00 and the cycle repeats.

Why is the frequency division in the counter called 'divide-by-2'?

-The frequency division is called 'divide-by-2' because each flip-flop in the circuit halves the frequency of its input signal. With two flip-flops, the input clock frequency (FC) is divided by 2 and then by 4 for each successive flip-flop.

How does adding more flip-flops affect the counting range and frequency division?

-Adding more flip-flops increases the counting range exponentially. Each additional flip-flop divides the frequency further by 2. For example, with four flip-flops, the frequency is divided by 16, and the counter can count from 0 to 15.

What is the significance of using the toggle mode (J = 1, K = 1) in JK flip-flops for counters?

-In toggle mode (J = 1, K = 1), the JK flip-flop switches between its two states (0 and 1) with each clock pulse. This behavior is essential for counters, as it ensures that the flip-flop alternates between states to keep track of the count.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

Dasar Sistem Digital | 09 - Register & Counter

Part 5.2 #Latches and #FlipFlops #SequentialCircuits in Digital Electronics in Hindi

O QUE É O FLIP FLOP? | Como Funcionam os Flip Flops JK, SR, D e T | Eletrônica Digital

Sistem Digital - Flip Flop D, JK dan T

Latches and Flip-Flops 6 - The JK Flip Flop

SAYISAL ELEKTRONİK DERSLERİ: JK Flip Flop

5.0 / 5 (0 votes)