Simulasi Rangkaian JK Flip-flop, RS Flip-flop, dan D Flip-flop ( Faishal Satria G 2211181006 )

Summary

TLDRThis video provides an in-depth explanation of flip-flop circuits, including RS flip-flop with clock, JK flip-flop, and D flip-flop. The host, Faisal, a student in Electrical Engineering, explains the theoretical concepts behind each flip-flop type, their truth tables, and their behaviors with clock inputs. Practical simulations using both basic logic gates and ICs are demonstrated, allowing viewers to see the circuits in action. The video aims to help students understand these fundamental digital components for their final exam in Digital Electronics.

Takeaways

- 😀 Introduction to the RS flip-flop with a clock, which differs from the regular RS flip-flop due to the presence of a clock input (C).

- 😀 The clock (C) input in an RS flip-flop allows the output to change only during certain clock transitions (positive or negative).

- 😀 In the RS flip-flop with a clock, when S=0 and R=1, the output Q=0, and Q' = 1 (Reset state).

- 😀 When S=1 and R=0 in an RS flip-flop, the output Q=1 and Q' = 0 (Set state).

- 😀 If both S and R are equal to 1 in an RS flip-flop, the output will be undefined or invalid.

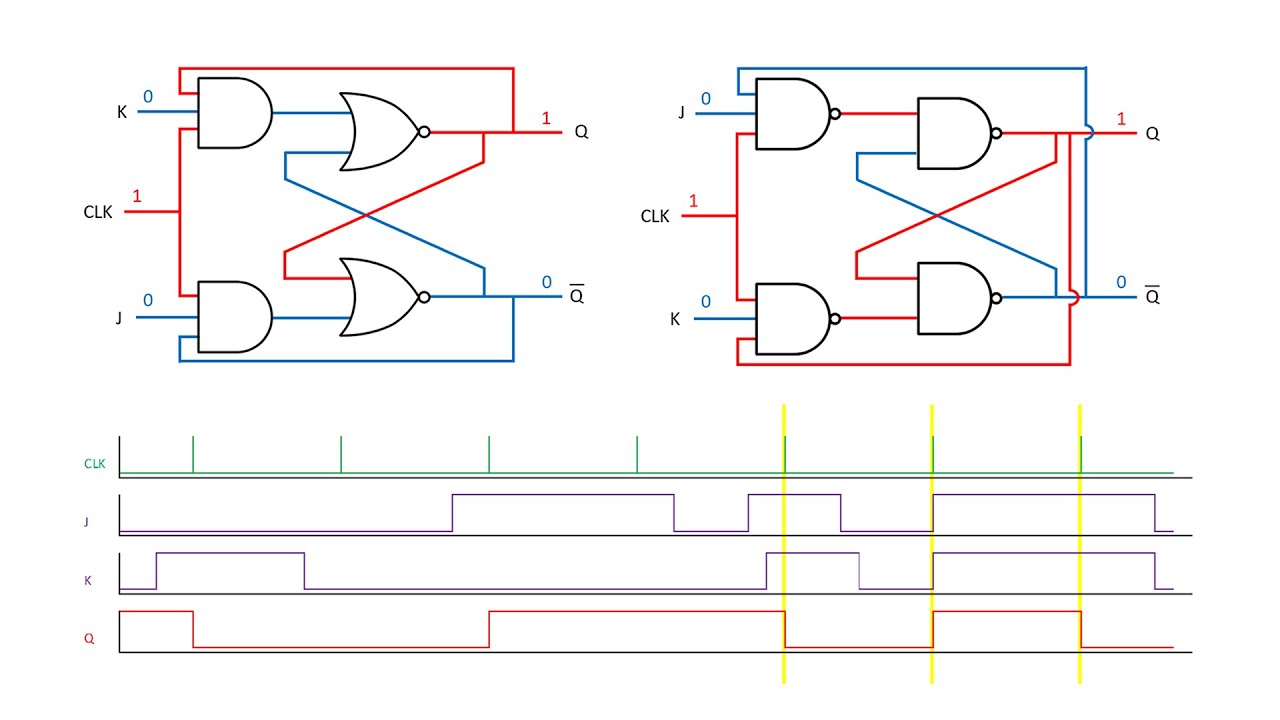

- 😀 JK flip-flops are a modification of RS flip-flops that resolve the invalid state when both inputs are 1, producing a toggle (T) behavior instead.

- 😀 The JK flip-flop consists of two RS flip-flops connected together: a master flip-flop and a slave flip-flop.

- 😀 In JK flip-flops, the T behavior means that the output will toggle (flip) when both J=1 and K=1, changing the output state.

- 😀 D flip-flops are simpler than JK flip-flops. The output Q always matches the input D during the positive clock edge.

- 😀 A key difference between flip-flop types is the handling of invalid or undefined states—JK flip-flops define behavior (toggle), while RS flip-flops do not.

- 😀 Practical simulations of the RS flip-flop, JK flip-flop, and D flip-flop are shown using both logic gates and ICs (TTL ICs) to demonstrate functionality.

Q & A

What is the main difference between RS Flip-Flop with a clock and the regular RS Flip-Flop?

-The main difference is the addition of a clock input in the RS Flip-Flop with a clock. This clock input controls the state change, making the output depend not only on the set (S) and reset (R) inputs but also on the clock signal. It introduces clock-driven behavior, which is not present in the regular RS Flip-Flop.

What happens when both inputs (S and R) are set to 0 in an RS Flip-Flop with a clock?

-When both inputs (S = 0, R = 0) are set to 0, the output remains unchanged, meaning the flip-flop's state stays the same (No Change).

What does the 'invalid' condition mean in an RS Flip-Flop with a clock?

-The 'invalid' condition occurs when both S and R are set to 1. This causes the output to be undefined or random, which is not a valid state for the flip-flop. It is a situation that should be avoided in practical circuits.

How does a JK Flip-Flop handle the situation where both inputs are 1, which causes an issue in the RS Flip-Flop?

-In a JK Flip-Flop, when both inputs (J and K) are set to 1, it does not cause an invalid state as in the RS Flip-Flop. Instead, the output toggles (flips), meaning if the output was 1, it becomes 0, and if it was 0, it becomes 1. This behavior is defined as 'toggle'.

What is the Master-Slave configuration in a JK Flip-Flop?

-The Master-Slave configuration in a JK Flip-Flop consists of two flip-flops: the Master and the Slave. The Master flip-flop operates when the clock signal is high (1), while the Slave flip-flop operates when the clock signal is low (0). This ensures that the output changes only during the appropriate clock edge, avoiding glitches.

What is the key difference between the JK Flip-Flop and the RS Flip-Flop with a clock?

-The key difference is that the JK Flip-Flop avoids the invalid state when both inputs are 1, whereas the RS Flip-Flop with a clock enters an invalid state under the same condition. In JK Flip-Flops, both inputs being 1 causes the output to toggle, while in RS Flip-Flops with a clock, the output becomes undefined.

How does a D Flip-Flop work, and how is it simpler than the JK Flip-Flop?

-A D Flip-Flop operates by ensuring that the output (Q) always follows the input (D) during the positive clock edge. This makes the D Flip-Flop simpler than the JK Flip-Flop, as it only requires a single input (D) to control the output, while the JK Flip-Flop has two inputs (J and K) with more complex behavior.

What is the function of the clock input in flip-flops like RS, JK, and D flip-flops?

-The clock input in flip-flops controls when the state of the flip-flop can change. It ensures that the output only changes at specific moments, usually during the transition of the clock signal (either rising or falling edge). This enables synchronized operation in sequential circuits.

What is the benefit of building flip-flop circuits with basic logic gates before using ICs like the 7400 series?

-Building flip-flop circuits with basic logic gates first helps in understanding the underlying behavior and connections of the circuit. Once the user is familiar with how the logic gates work together, using ICs like the 7400 series becomes easier, as the internal connections are abstracted, but the fundamental operation remains the same.

What did the speaker demonstrate in the video to show how flip-flops behave in simulations?

-The speaker demonstrated the behavior of various flip-flops, including RS, JK, and D flip-flops, by simulating them using both basic logic gates and ICs like the 7400 series. The simulations were performed to show the output behavior for different input conditions, confirming the theoretical truth tables.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade Now5.0 / 5 (0 votes)