Simulating Verilog Designs in Quartus and Modelsim using Testbenches - Essential design flow.

Summary

TLDRThis tutorial guides users through the process of creating and simulating a Verilog testbench using Quartus and ModelSim. It covers everything from writing a simple 4-bit counter module to generating a clock signal, instantiating the module within a testbench, and running simulations. Key steps include setting up the testbench as the top-level entity, handling common errors, and monitoring simulation results in ModelSim. The video also explains how to expand the design by adding more modules, demonstrating how to create complex designs and troubleshoot issues during simulation. Ideal for beginners looking to understand Verilog simulation workflows.

Takeaways

- 😀 Ensure that your Verilog module is saved in the project folder and appears in the Project Navigator to make it available for instantiation in other modules.

- 😀 A testbench in Verilog is a top-level module designed specifically for testing other modules. It generates signals and applies them to the module under test.

- 😀 Always define a time scale and precision in your testbench. The time scale dictates the simulation time unit, and the precision determines the time step in the simulation.

- 😀 When writing a testbench, the clock signal is usually generated in an always block. It toggles between 0 and 1, with a defined delay that determines the clock frequency.

- 😀 The testbench should instantiate the module to be tested. This can be done manually or through Quartus' 'Create Verilog Instantiation Template' feature to save time.

- 😀 Always ensure the module instantiation names and signal names in your testbench match those defined in the module you're testing (e.g., 'clock' and 'count').

- 😀 In a testbench, input signals are often declared as registers (e.g., clock), while output signals are typically declared as wires (e.g., count).

- 😀 Before running simulations, ensure that your testbench is set as the top-level entity in Quartus and that all necessary simulation settings are configured.

- 😀 Common errors in Verilog simulation include incorrect signal assignments or mismatched module ports. Be sure to resolve errors quickly to avoid simulation failures.

- 😀 ModelSim can be used to run RTL simulations and view waveforms. Use zoom functions to inspect specific signal transitions, like the counter incrementing over time.

Q & A

What is the purpose of the test bench in Verilog simulation?

-The purpose of the test bench in Verilog simulation is to instantiate and test other Verilog modules by generating stimuli (inputs) and monitoring the outputs to verify the functionality of the design being tested.

Why is it important to register the test bench in Quartus?

-It is important to register the test bench in Quartus because it ensures that Quartus recognizes the test bench as the top-level entity, allowing it to simulate the design correctly and providing the necessary connections for the simulation environment.

How does the time scale affect the Verilog simulation?

-The time scale in Verilog defines the precision of time intervals used in the simulation. It sets the length of one time tick, and the simulation timing is based on this scale. A correct time scale ensures accurate simulation behavior.

What is the difference between a reg and a wire in Verilog?

-In Verilog, a 'reg' is used for variables that store values and can be assigned within procedural blocks (like 'always'), while a 'wire' represents a continuous connection between modules and is driven by an external source or output of another module.

How do you instantiate a Verilog module within a test bench?

-To instantiate a Verilog module within a test bench, you need to use the module name, provide necessary ports, and connect the module’s inputs and outputs to signals defined in the test bench. This can be done manually or with an instantiation template.

What is the purpose of the always block in the test bench?

-The 'always' block in the test bench is used to generate repeating signals, such as a clock, by continuously executing a set of statements. In the case of a clock, the 'always' block toggles the clock signal at regular intervals.

How do you handle errors during simulation in Quartus and ModelSim?

-To handle errors during simulation, carefully read the error messages provided by Quartus or ModelSim. Errors often point to issues like mismatched signal names, incorrect syntax, or incorrect module instantiation. Fixing these errors involves checking your code for consistency and ensuring that all necessary connections are made.

Why is it important to use the correct clock signal name when instantiating a module?

-Using the correct clock signal name is important because mismatching the signal names between the test bench and the module can cause simulation errors. The clock signal in the test bench must match the clock input port of the instantiated module.

What does the 'processing start analysis and elaboration' step do in Quartus?

-The 'processing start analysis and elaboration' step in Quartus compiles and elaborates the design files. It checks for syntax errors, resolves dependencies, and prepares the design for simulation or hardware implementation.

How can you visualize and analyze the simulation results in ModelSim?

-In ModelSim, you can visualize and analyze simulation results by opening the **Wave** window, which displays the signal transitions over time. You can zoom in on specific areas of the simulation and change the radix to view signal values in different formats, such as binary or decimal.

Outlines

此内容仅限付费用户访问。 请升级后访问。

立即升级Mindmap

此内容仅限付费用户访问。 请升级后访问。

立即升级Keywords

此内容仅限付费用户访问。 请升级后访问。

立即升级Highlights

此内容仅限付费用户访问。 请升级后访问。

立即升级Transcripts

此内容仅限付费用户访问。 请升级后访问。

立即升级浏览更多相关视频

MULTIPLEXER 4 : 1 VERILOG CODE ON XILINX

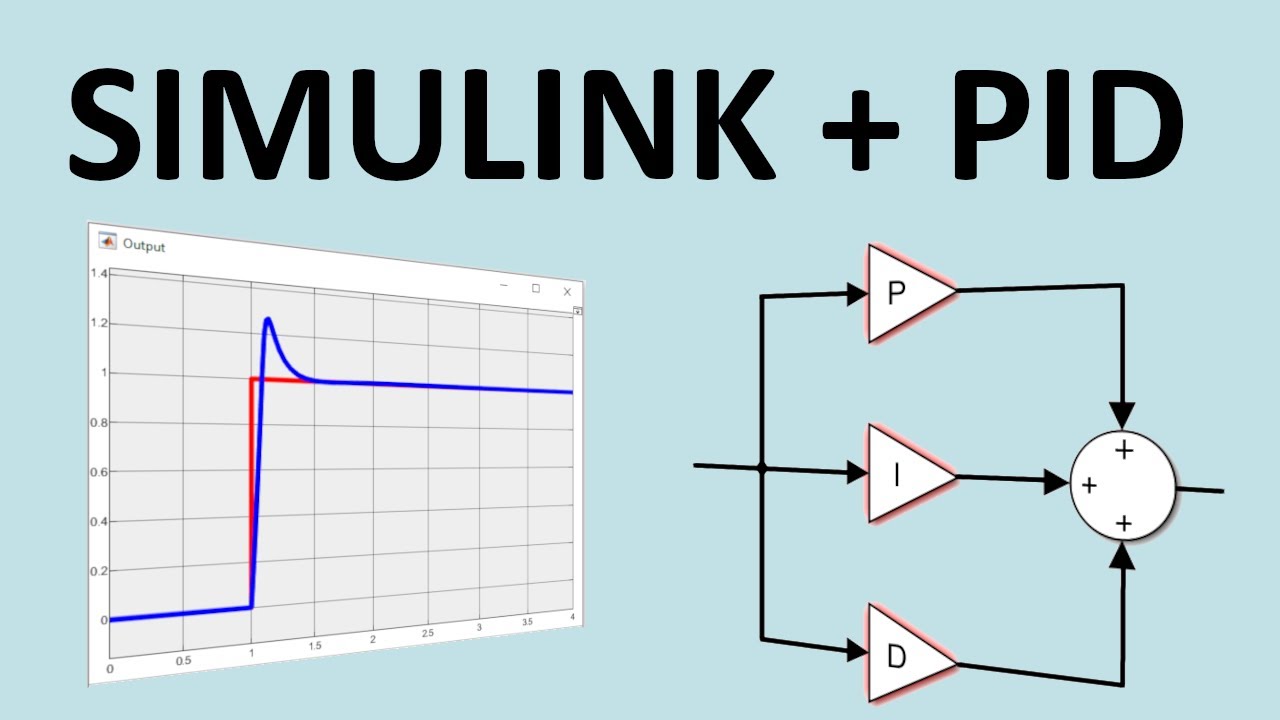

Simulink Control Systems and PID, Matlab R2020b

Vue Unit Testing #2 - Button component test

Washing Machine using Verilog (with code) | Verilog HDL Project by @Dhaval Gupta | FSM | Vivado

Moore Machine Verilog Implementation on Xilinx: ISE D Suite | Digital Design

Tutorial Mastercam X5 CNC Mill / Fraish

5.0 / 5 (0 votes)