Latches and Flip-Flops 2 - The Gated SR Latch

Summary

TLDRThis script explains the concept of a gated SR latch, an advanced version of the basic SR latch, which can only change state when enabled. It uses the analogy of an air conditioning system to illustrate how each room's cooling unit can be independently controlled by its own SR latch. The video describes how to convert a regular SR latch into a gated one by adding AND or NAND gates, creating an additional 'enable' input. It also introduces the symbol for a gated SR latch and uses timing diagrams to demonstrate its behavior, highlighting its utility in various applications.

Takeaways

- 🔒 A gated SR latch is an SR latch with an additional 'enable' functionality, allowing it to change state only when enabled.

- 🏢 The concept is illustrated with an air conditioning system, where each room's cooling unit is controlled by an SR latch with set/reset signals from sensors.

- 🔄 An SR latch is level-sensitive, meaning it responds to the level of the input signal (high or low) rather than the duration of the pulse.

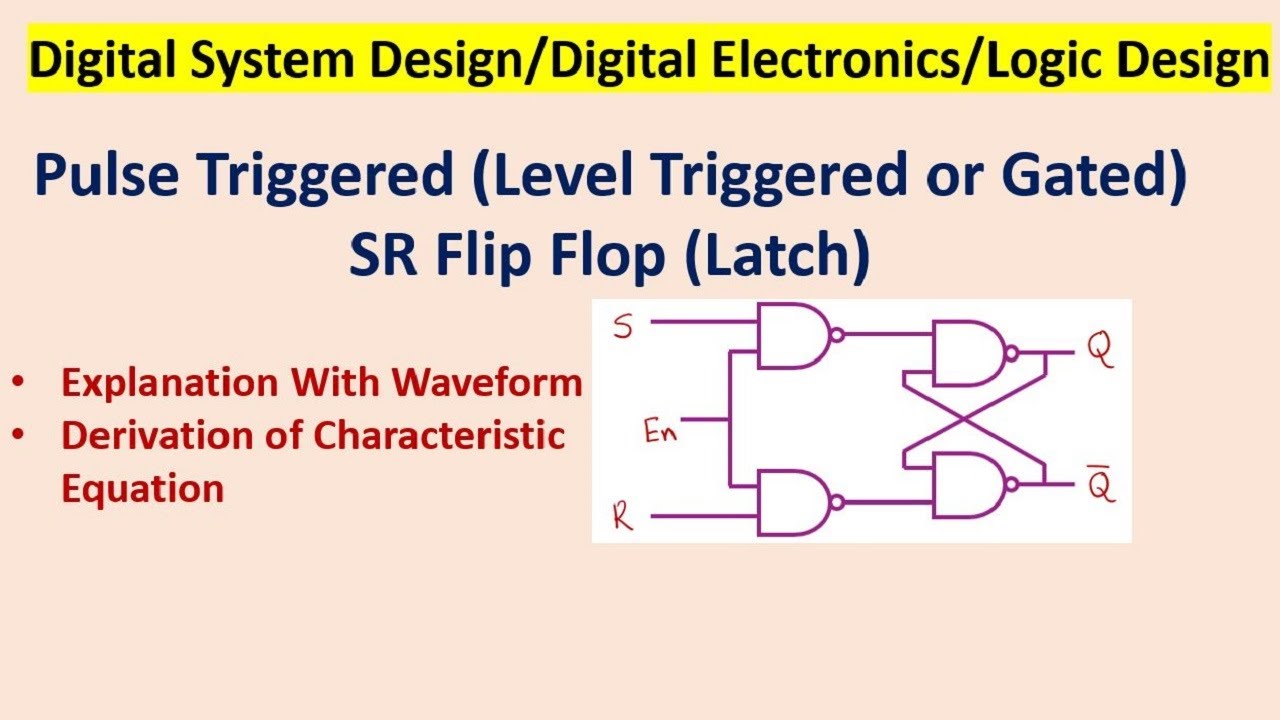

- 🛠️ To create a gated SR latch, AND gates are added to an SR latch built from NOR gates, or additional NAND gates are added for one built from NAND gates.

- 🔄 The addition of gates changes the latch from active low to active high, depending on the type of gates used (NOR or NAND).

- 🚫 It's invalid for both S and R inputs to be high at the same time in an SR latch.

- 🔑 The third input 'E' in a gated SR latch is crucial as it enables or disables the latching effect.

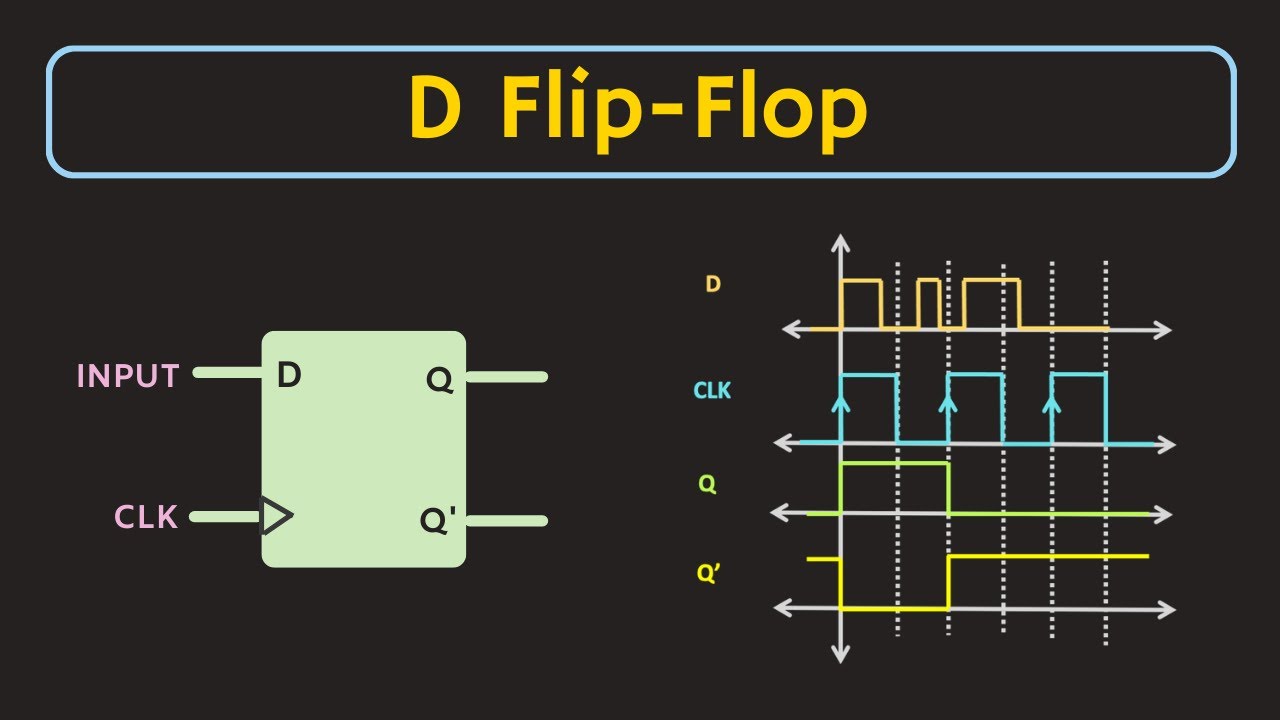

- 📊 The behavior of a latch can be visualized using a timing diagram, which shows changes in voltage over time for each input and the output.

- 🔄 The normal states of S and R are reversed when transforming an active low latch into an active high latch using additional gates.

- 🔄 The term 'steering gates' refers to the additional gates that create the gated functionality in an SR latch.

- 👁️ A transparent latch allows input to affect the output unconditionally, whereas a gated SR latch is transparent only when enabled.

Q & A

What is a gated set/reset latch?

-A gated set/reset latch is an SR latch that can only change state when it is enabled. It incorporates an additional input, 'E', which acts as an enable signal to control the latching effect.

How can a gated SR latch be used in an air conditioning system?

-In an air conditioning system, each room could have its own cooling unit controlled by an SR latch. The set and reset signals might come from temperature or humidity sensors, and a central control panel could enable or disable these units on a room-by-room basis.

What is an active high SR latch?

-An active high SR latch is one that requires a high pulse (1) at input S to set the latch and a high pulse at input R to reset it, resulting in a high output at Q.

What does it mean for an SR latch to be level sensitive?

-A level-sensitive SR latch responds to a valid change in either S or R, regardless of the duration of the input pulse. It is the level (high or low) that matters, not the duration of the input.

How can an SR latch be made into a gated SR latch?

-A regular SR latch can be turned into a gated SR latch by connecting a pair of AND gates in series with the inputs of an OR-based SR latch, or by adding another pair of NAND gates to a NAND-based SR latch.

What is the purpose of the steering gates in a gated SR latch?

-Steering gates, which are the additional AND or NAND gates in a gated SR latch, control the transparency of the latch. They determine whether the latch will respond to changes in S or R inputs only when enabled.

What is the difference between a transparent and a gated SR latch?

-A transparent SR latch is one where a valid input will affect the output unconditionally. A gated SR latch, on the other hand, is transparent only when it is enabled by the additional input E.

What symbol is used to represent a gated SR latch in diagrams?

-A gated SR latch has its own symbol that simplifies diagrams, showing inputs SE and R, the output Q, and its inverse, to focus on what the latch does rather than the internal components.

How can the behavior of a latch be described using a timing diagram?

-The behavior of a latch can be described using a timing diagram that shows changes in voltage against time for each input (S, R, E) and the output Q, allowing visualization of the circuit's operation over time.

How does the enable input 'E' affect the behavior of a gated SR latch?

-The enable input 'E' determines whether the gated SR latch will respond to changes in S or R. If 'E' is high, the latch is enabled and will change state based on S and R inputs; if 'E' is low, the latch is disabled and will not respond to S or R inputs.

What is the significance of the transition time in a digital circuit?

-The transition time, which is the time it takes for the voltage to change from low to high or vice versa, is significant in digital circuits. Although it is assumed to be instantaneous in the script for simplicity, in reality, it takes a few nanoseconds and can affect circuit performance.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

SR Latch and Gated SR Latch Explained | SR Latch using NOR gates and NAND gates

Pulse Triggered (Level Triggered or Gated) SR Flip Flop (Latch)

D Flip-Flop Explained | Truth Table and Excitation Table of D Flip-Flop

Latches and Flip-Flops 1 - The SR Latch

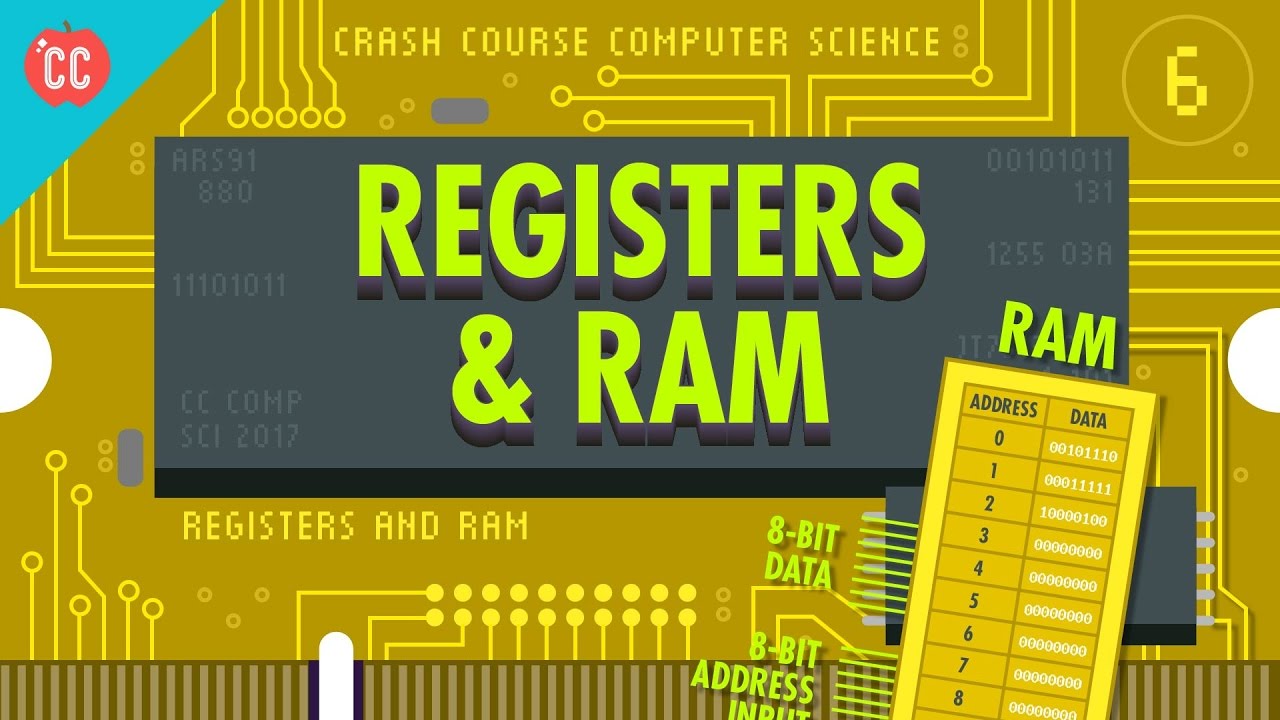

Registers and RAM: Crash Course Computer Science #6

Clocked SR Flip Flop using NAND Gates with Truth Table and Circuit Diagram

5.0 / 5 (0 votes)