SR Latch and Gated SR Latch Explained | SR Latch using NOR gates and NAND gates

Summary

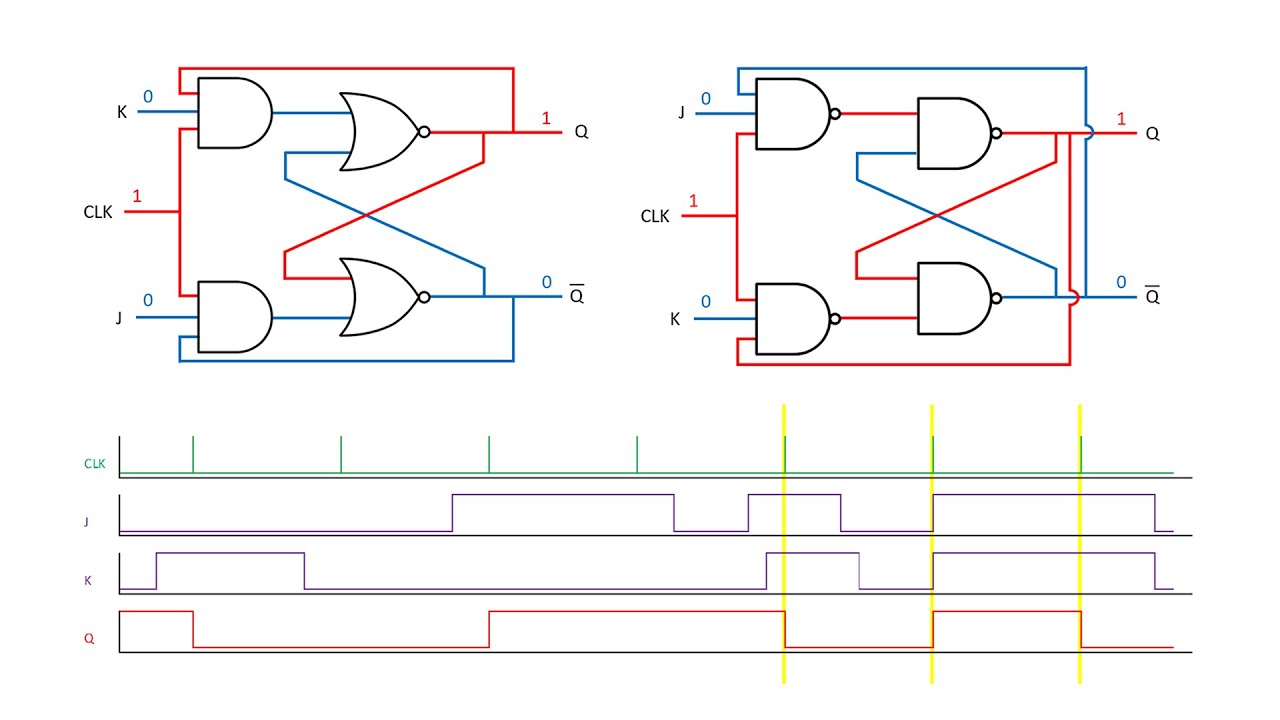

TLDRThis video from the ALL ABOUT ELECTRONICS YouTube channel delves into the world of latches, focusing on the SR latch. It explains the basic design and operation of the SR latch, which uses feedback to store binary information. The video contrasts it with a gated SR latch, which adds an enable input for controlled input response. Both NOR and NAND gate implementations are discussed, along with their truth tables. The video concludes with the gated SR latch's operation under a periodic clock signal, demonstrating its use as a synchronous memory element, and hints at the advantages of flip-flops in sequential circuits, a topic for the next video.

Takeaways

- 😀 The video discusses the concept of latches and flip-flops, focusing on the SR latch and its variations.

- 🔧 The basic SR latch is constructed using two NOT gates with feedback loops, allowing it to store binary information.

- 🛠️ The SR latch can be implemented using NOR gates, where the outputs are connected to form a bistable circuit with two stable states.

- 🔄 The SR latch has two inputs, 'Set' (S) and 'Reset' (R), which are used to set or reset the stored information.

- ❌ A forbidden condition for the SR latch is when both S and R inputs are high, as it leads to an indeterminate output state.

- 🔀 The video explains how to design an SR latch using NAND gates, which has active low inputs and a different truth table compared to the NOR gate version.

- 🚦 The gated SR latch is introduced as a variation that includes an 'Enable' input, controlling when the latch responds to the S and R inputs.

- 🔄 The gated SR latch can be built from a standard SR latch by adding AND or NAND gates, making it controllable and suitable for synchronous operation.

- ⏲️ By applying a clock signal to the enable input, the gated SR latch can act as a synchronous memory element, responding to input changes only when the clock is high.

- 🔑 The video concludes with a teaser for the next episode, which will cover why flip-flops are more suitable for synchronous circuits and introduce the SR flip-flop.

Q & A

What is the main difference between a latch and a flip-flop?

-The main difference between a latch and a flip-flop is that a latch can change its state as soon as the input changes, whereas a flip-flop changes its state only at specific clock times.

What is an SR latch and how is it different from other types of latches?

-An SR latch is a basic type of bistable multivibrator circuit that has two stable states and can be set or reset using separate inputs labeled S (Set) and R (Reset). It is different from other types of latches in that it does not have an enable or clock input, making it an asynchronous memory element.

How does the feedback mechanism in an SR latch work?

-In an SR latch, the feedback mechanism involves the outputs of the cross-coupled gates being fed back to the inputs. This creates a loop that maintains the state of the latch until an input change occurs, allowing the latch to store one bit of information.

What are the two inputs of an SR latch and what do they do?

-The two inputs of an SR latch are S (Set) and R (Reset). The Set input, when high, sets the output to a high state, storing a binary '1', while the Reset input, when high, resets the output to a low state, storing a binary '0'.

Why is the condition where both S and R inputs of an SR latch are high considered forbidden?

-The condition where both S and R inputs are high is forbidden because it results in both outputs being low, which violates the complementary nature of the outputs. This condition can lead to unpredictable behavior and is thus avoided.

How can an SR latch be designed using NOR gates?

-An SR latch can be designed using NOR gates by cross-coupling two NOR gates and connecting the output of one gate to the input of the other, with the S and R inputs determining the state of the latch based on the truth table of the NOR gate.

What is a gated SR latch and how does it differ from a standard SR latch?

-A gated SR latch is a variant of the SR latch that includes an additional enable input. Unlike the standard SR latch, which responds immediately to input changes, the gated SR latch only responds when the enable input is high, making it suitable for synchronous operations.

How does the enable input affect the operation of a gated SR latch?

-The enable input of a gated SR latch controls when the latch will respond to the S and R inputs. When the enable input is high, the latch behaves like a normal SR latch, responding to input changes. When the enable input is low, the latch retains its current state, ignoring input changes.

What is the significance of the truth table in understanding the operation of an SR latch?

-The truth table of an SR latch is significant because it provides a clear representation of the latch's behavior for all possible input combinations. It helps in understanding how the latch will respond to different inputs and what outputs to expect, which is crucial for designing and troubleshooting digital circuits.

Can a gated SR latch be used as a synchronous memory element? If so, how?

-Yes, a gated SR latch can be used as a synchronous memory element by applying a periodic clock signal to its enable input. During the high phase of the clock, the latch becomes transparent to inputs, and during the low phase, it retains its state, making it sensitive to the clock level.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

Latch and Flip-Flop Explained | Difference between the Latch and Flip-Flop

Latches and Flip-Flops 6 - The JK Flip Flop

Part 5.2 #Latches and #FlipFlops #SequentialCircuits in Digital Electronics in Hindi

Latches and Flip-Flops 2 - The Gated SR Latch

Semiconductor Memories: ROM Explained | Types of ROM | Applications of ROM

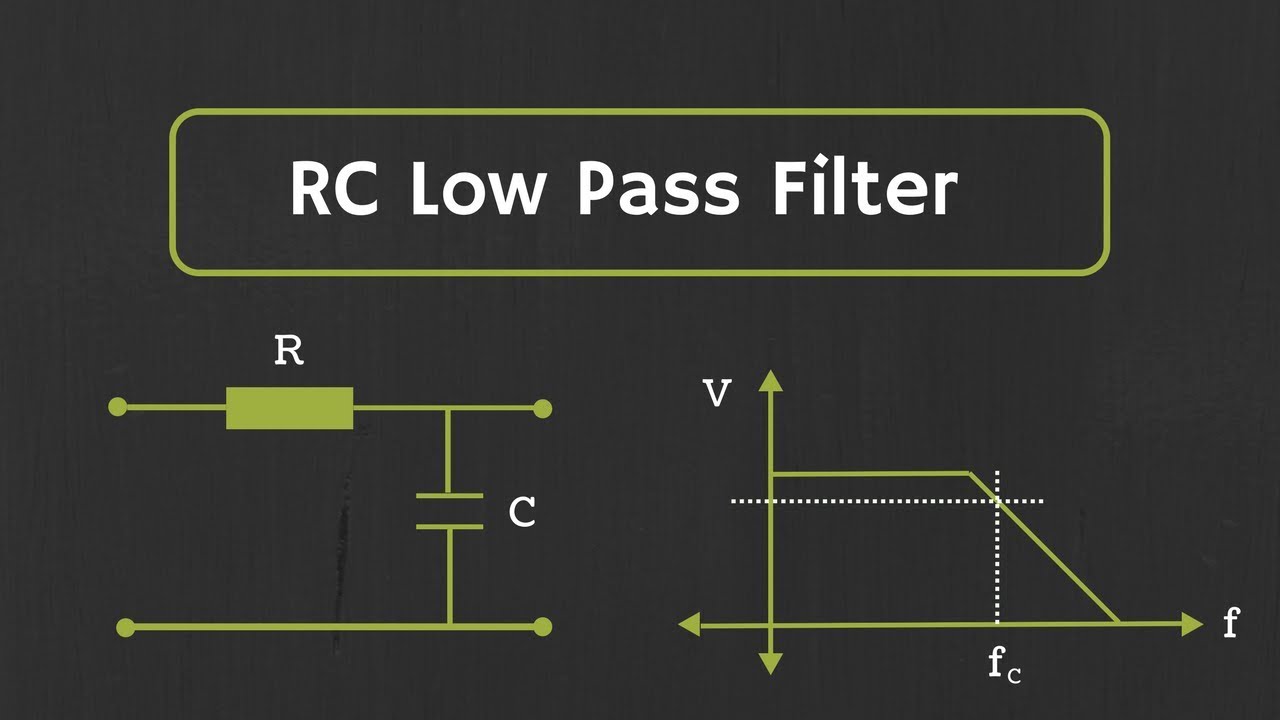

RC Low Pass Filter Explained

5.0 / 5 (0 votes)