Verification d(data) flip flop using sv-uvm.

Summary

TLDRThis video delves into the verification of a D Flip-Flop (DFF) using SystemVerilog and UVM, detailing the complete testbench architecture. It introduces essential components like the driver, sequencer, and monitor, which work together to apply stimulus and capture output for comparison. The sequences created simulate various conditions, ensuring the DFF operates correctly under different scenarios. The video concludes with successful verification results, emphasizing the effectiveness of UVM for sequential circuit testing while hinting at future explorations of Mod ports, clocking blocks, and virtual sequences.

Takeaways

- 😀 UVM (Universal Verification Methodology) is essential for verifying sequential circuits like D flip-flops.

- 🔍 The verification process involves creating a comprehensive testbench architecture that includes various components.

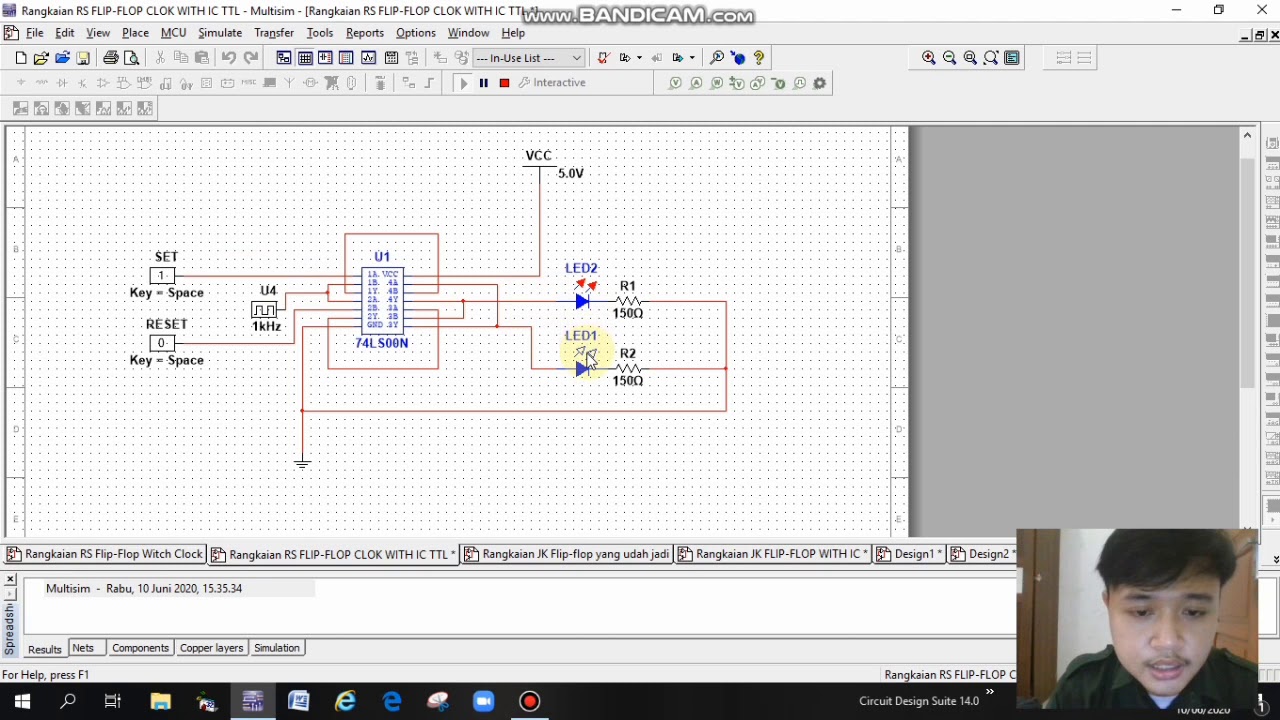

- ⚙️ The top-level testbench instantiates the D flip-flop and configures a virtual interface for DUT interaction.

- 🧩 Key components of the testbench architecture include the driver, monitor, and scoreboard.

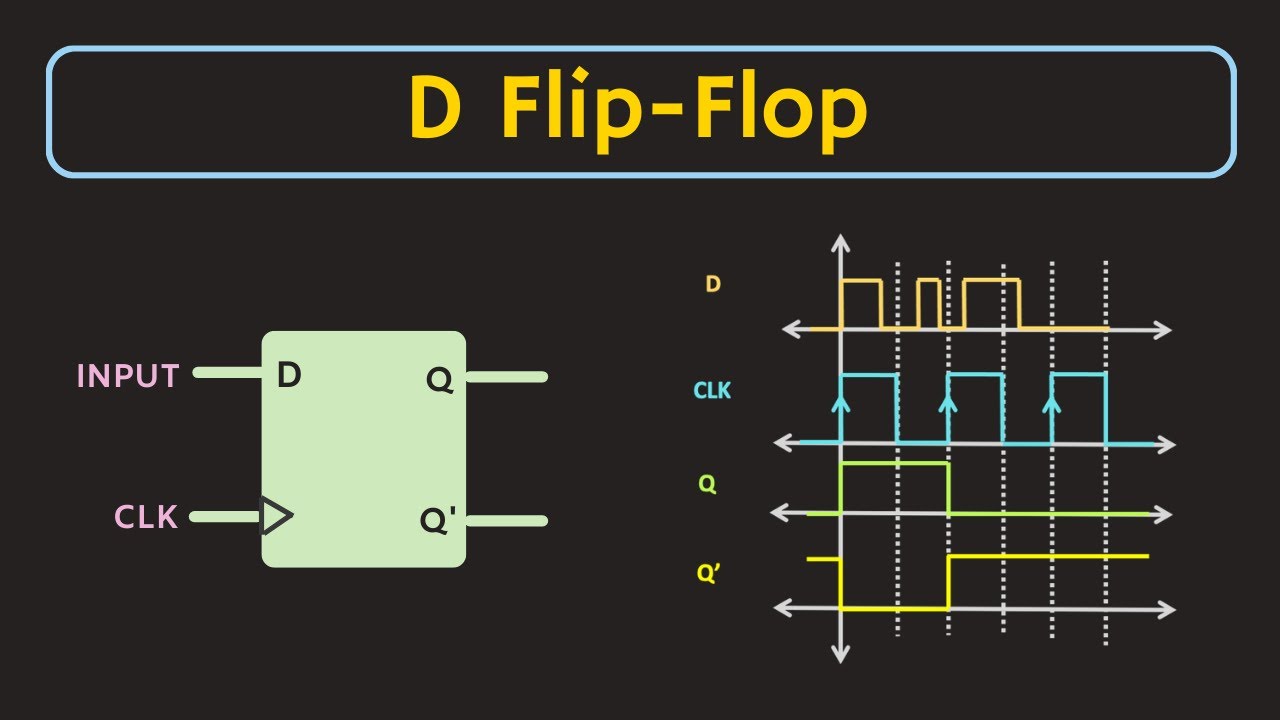

- 🔄 The driver is responsible for sending stimulus to the DUT, effectively controlling input signals.

- 📊 The monitor captures output data from the DUT and communicates it to the scoreboard for validation.

- ✅ The scoreboard compares expected results against actual DUT outputs to determine test pass/fail status.

- 📜 Specific sequence classes are created to manage the input patterns applied to the DUT during testing.

- 🔄 The D flip-flop operates based on clock edges and is controlled by reset and D inputs.

- 🌟 Future explorations include enhancing the D flip-flop with mod ports and clocking blocks to further improve verification capabilities.

Q & A

What is the primary focus of the video?

-The primary focus of the video is to explain the verification process of a sequential circuit using UVM (Universal Verification Methodology).

What does a passing state indicate in the verification process?

-A passing state indicates that the output of the circuit matches the expected result, confirming that the verification has been successful.

What is meant by 'D free flow' in the context of this video?

-'D free flow' refers to a specific verification scenario for a D-type flip-flop, where the output behavior is analyzed without interference from other signals.

What upcoming topics will be covered in the next video?

-The next video will cover the D5 configuration, focusing on Mod ports, clocking blocks, and the introduction of virtual sequences.

Why is UVM important for verifying sequential circuits?

-UVM provides a standardized methodology for verifying complex designs, ensuring that all aspects of a sequential circuit are thoroughly tested and validated.

What role do Mod ports and clocking blocks play in circuit verification?

-Mod ports and clocking blocks help manage the timing and interaction of signals within a design, ensuring accurate representation and behavior during verification.

How can viewers further explore the concepts discussed in the video?

-Viewers can explore the concepts by studying the example provided in the video and applying UVM techniques to their own verification projects.

What is a virtual sequence in the context of UVM?

-A virtual sequence is a UVM construct that allows for the coordination of multiple sequences, enabling complex interactions among various components of the design.

What does the speaker hope the audience gained from the video?

-The speaker hopes the audience gained a clear understanding of UVM verification processes for sequential circuits and enjoyed the educational content.

What is the significance of the output being equal to 0 in the verification process?

-The output being equal to 0 signifies that the circuit has performed as expected, thereby validating the verification process and confirming correct functionality.

Outlines

Esta sección está disponible solo para usuarios con suscripción. Por favor, mejora tu plan para acceder a esta parte.

Mejorar ahoraMindmap

Esta sección está disponible solo para usuarios con suscripción. Por favor, mejora tu plan para acceder a esta parte.

Mejorar ahoraKeywords

Esta sección está disponible solo para usuarios con suscripción. Por favor, mejora tu plan para acceder a esta parte.

Mejorar ahoraHighlights

Esta sección está disponible solo para usuarios con suscripción. Por favor, mejora tu plan para acceder a esta parte.

Mejorar ahoraTranscripts

Esta sección está disponible solo para usuarios con suscripción. Por favor, mejora tu plan para acceder a esta parte.

Mejorar ahoraVer Más Videos Relacionados

5.0 / 5 (0 votes)