ARM7 Interrupts and Exceptions: Steps, ISR Address, and Overview | ARM

Summary

TLDRThis video explains how interrupts and interrupt service routines (ISRs) are managed in ARM7 processors. It details the steps involved in interrupt handling, including saving the program state, switching to interrupt modes, executing ISRs, and restoring the main program after interrupt service. The video also covers ARM7's task switching, interrupt priorities, and mode-specific operations, emphasizing how each interrupt (e.g., IRQ, FIQ) is handled based on its priority. This comprehensive guide provides insights into ARM7's architecture and interrupt management for students and enthusiasts.

Takeaways

- 😀 ARM7 interrupts, also referred to as exceptions, are explained in terms of how they trigger different modes and affect the execution of the main program.

- 😀 When an interrupt occurs, the ARM7 processor suspends the main program and executes an Interrupt Service Routine (ISR), returning to the main program afterward.

- 😀 The Current Program Status Register (CPSR) stores the status of the main program, and its value must be preserved when handling interrupts.

- 😀 Before servicing an interrupt, the CPSR is saved into the Saved Program Status Register (SPSR) to ensure that the main program's state remains intact.

- 😀 The ARM7 processor operates in different modes, each with its own SPSR. The mode triggered by the interrupt is determined by bits in the CPSR.

- 😀 Interrupts are serviced in ARM state with 32-bit instructions. The processor's T-bit is cleared to ensure correct ISR execution.

- 😀 The Program Counter (PC) from the main program is saved into the Link Register (LR) so the interrupt handler can return to the correct location after ISR execution.

- 😀 Each interrupt mode has a defined ISR address, with branch instructions used to jump to the ISR code. Fast Interrupt (FIQ) has a higher priority and executes faster due to fewer steps and dedicated registers.

- 😀 ARM7 prioritizes interrupts. Reset has the highest priority, followed by data aborts, FIQ, IRQ, prefetch aborts, and software interrupts (SWI).

- 😀 Task switching in ARM7 TDMI follows the same principles as interrupt handling, with tasks assigned to specific modes and corresponding interrupt service steps.

- 😀 ISRs are generally small and only a few bytes in size, as they mainly contain branch instructions that direct the processor to the actual ISR program code.

Q & A

What is the main topic covered in this video?

-The main topic of the video is the explanation of interrupts (or exceptions) in the ARM7 processor, focusing on how interrupt service routines (ISRs) are handled.

What happens when an interrupt occurs while the main program is running?

-When an interrupt occurs during the main program execution, ARM7 suspends the main program, services the interrupt through the ISR, and then returns to the main program at the exact location where the interrupt occurred.

What is the purpose of the CPSR and SPSR in the interrupt handling process?

-The CPSR (Current Program Status Register) holds the status of the main program, while the SPSR (Saved Program Status Register) stores the CPSR value before interrupt handling begins. This ensures that the program's state is preserved and restored after servicing the interrupt.

How does ARM7 ensure that the main program resumes from the correct location after an interrupt?

-ARM7 saves the program counter (PC) of the main program into the link register (LR) of the interrupt mode. Once the ISR is completed, ARM7 restores the PC from LR to return to the exact location in the main program where the interrupt occurred.

Why is the T bit set to 0 during ISR execution in ARM7?

-The T bit is set to 0 to ensure that ARM7 uses 32-bit instructions in ARM state for the execution of the interrupt service routine. This is important for consistent execution during the ISR.

What role does the Link Register (LR) play in the interrupt handling process?

-The Link Register (LR) is used to store the address of the main program’s PC (program counter) before the interrupt. This allows ARM7 to return to the correct location in the main program after the ISR completes.

How does ARM7 handle multiple types of interrupts?

-ARM7 uses different interrupt modes for each interrupt type. Each interrupt type (e.g., reset, IRQ, FIQ) has its own predefined ISR address, and ARM7 enters the appropriate mode for handling that interrupt.

What is the priority order of interrupts in ARM7?

-The priority order of interrupts in ARM7 is as follows: 1. Reset (highest priority), 2. Data Abort, 3. FIQ (Fast Interrupt Request), 4. IRQ, 5. Prefetch Abort, 6. Undefined Instruction and Software Interrupt (SWI).

What is the significance of the fixed ISR address in ARM7?

-Each interrupt type in ARM7 has a fixed ISR address, which is the location where the program control jumps to service the interrupt. The ISR address allows ARM7 to execute the appropriate response for that interrupt.

How is the execution of the FIQ interrupt different from other interrupts?

-FIQ (Fast Interrupt Request) is processed faster than other interrupts because it does not require a branch instruction in its ISR. Additionally, FIQ has dedicated registers, making its execution more efficient.

Outlines

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenMindmap

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenKeywords

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenHighlights

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenTranscripts

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenWeitere ähnliche Videos ansehen

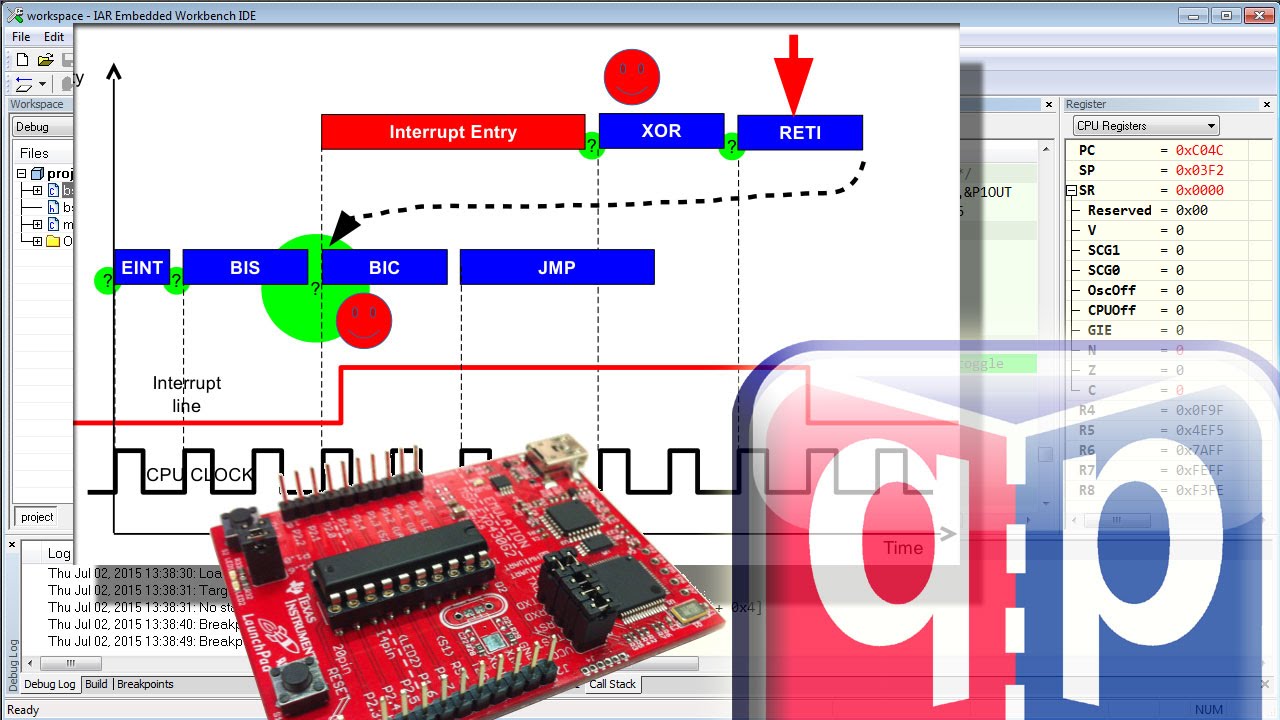

#17 interrupts Part-2: How most CPUs (e.g. MSP430) handle interrupts?

Arduino Workshop - Chapter 5 - Interrupts

Introduction to RTOS Part 9 - Hardware Interrupts | Digi-Key Electronics

RET & RETI Instructions of 8051 Microcontroller: Comparison and Explanation | Instructions of 8051

Operating System #14 What is an Interrupt? Types of Interrupts

50. CAMBRIDGE IGCSE (0478-0984) 4.1 Interrupts

5.0 / 5 (0 votes)