SR Latch and Gated SR Latch Explained | SR Latch using NOR gates and NAND gates

Summary

TLDRIn diesem Video wird der SR-Latch und der gated SR-Latch erklärt. Der SR-Latch reagiert sofort auf Eingangssignale und ist ein asynchrones Speicherelement. Der gated SR-Latch hingegen nutzt ein Taktssignal und wird dadurch zu einem synchronen Speicherelement, das nur bei aktiviertem Takt auf Eingaben reagiert. Der Ablauf eines gated SR-Latch wird anhand eines Timing-Diagramms veranschaulicht, bei dem der Latch seine Zustände basierend auf den Eingaben und dem Taktsignal beibehält. Der Videoautor erläutert auch, warum der gated SR-Latch für sequenzielle Schaltungen nicht ideal ist und verweist auf den nächsten Teil, in dem das Flip-Flop als bessere Option für synchrone Schaltungen vorgestellt wird.

Takeaways

- 😀 Der SR-Latch ist ein asynchrones Speicherelement, das sofort auf Änderungen der Eingaben reagiert.

- 😀 Ein SR-Latch kann mit NAND- oder NOR-Gattern realisiert werden, wobei die Eingabe 'Set' und 'Reset' den Zustand des Ausgangs steuern.

- 😀 Ein ungültiger Zustand entsteht, wenn sowohl 'Set' (S) als auch 'Reset' (R) gleichzeitig aktiv sind, daher wird dieser Zustand vermieden.

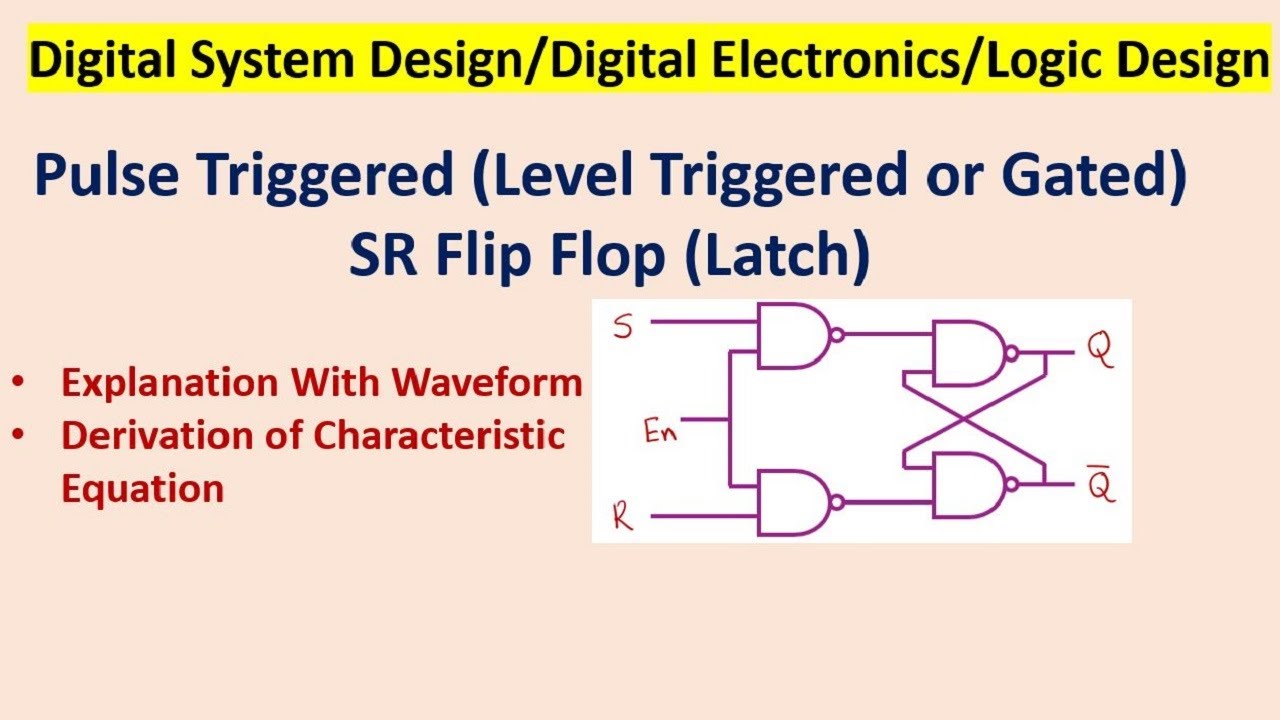

- 😀 Der Gated SR-Latch enthält ein zusätzliches Enable-Signal, das den Latch nur dann transparent macht, wenn es aktiv ist.

- 😀 Ein Gated SR-Latch kann als synchrones Speicherelement verwendet werden, da es nur auf Eingaben während eines hohen Enable-Signals reagiert.

- 😀 Während der Zeit, in der das Enable-Signal niedrig ist, behält der Gated SR-Latch seinen aktuellen Zustand bei.

- 😀 Der Gated SR-Latch wird durch das Enable-Signal gesteuert, das als Taktgeber fungiert, um Eingaben nur dann zuzulassen, wenn das Signal hoch ist.

- 😀 Die zeitliche Diagramm zeigt, wie der Gated SR-Latch auf Eingaben reagiert, wenn der Takt hoch oder niedrig ist.

- 😀 Das Setzen des Ausgangs (Q) auf hoch oder niedrig wird durch die Kombination der Eingaben 'Set' und 'Reset' sowie des Enable-Signals bestimmt.

- 😀 Der Gated SR-Latch ist in synchronen Schaltungen nicht bevorzugt, da er möglicherweise Timing-Probleme verursacht, weshalb Flip-Flops in solchen Anwendungen bevorzugt werden.

Q & A

Was ist der Zweck eines gated SR-Latch?

-Ein gated SR-Latch dient als speichernde Schaltung, die den Zustand basierend auf den Eingängen Set (S) und Reset (R) speichert, wobei der Enable-Eingang die Schaltung aktiviert oder deaktiviert, um auf diese Eingaben zu reagieren.

Wie wird ein SR-Latch mit NAND-Gattern realisiert?

-Das SR-Latch kann durch die Verbindung von zwei NAND-Gattern so aufgebaut werden, dass es mit den Eingängen S und R funktioniert, wobei der Ausgang Q durch die Zustände dieser Eingänge und des Enable-Signals beeinflusst wird.

Warum ist der Zustand, bei dem sowohl S als auch R gleichzeitig 1 sind, verboten?

-Wenn sowohl S als auch R gleichzeitig 1 sind, befinden sich beide Ausgänge Q und Q' im gleichen Zustand, was zu einem undefinierten Ausgang führt. Dieser Zustand wird daher als verboten angesehen, um die Schaltung stabil zu halten.

Wie verhält sich das gated SR-Latch, wenn das Enable-Signal hoch ist?

-Wenn das Enable-Signal hoch ist, wird das gated SR-Latch transparent und reagiert direkt auf die Eingänge S und R. Der Ausgang Q wird je nach Kombination der Eingänge gesetzt oder zurückgesetzt.

Was passiert mit dem Ausgang des gated SR-Latch, wenn das Enable-Signal niedrig wird?

-Wenn das Enable-Signal niedrig wird, bleibt der Ausgang des gated SR-Latch unverändert, selbst wenn sich die Eingänge S und R ändern. Die Schaltung speichert den letzten Zustand, bis das Enable-Signal wieder hoch wird.

Wie funktioniert das gated SR-Latch als synchrones Speicherelement?

-Durch das Anlegen eines periodischen Taktsignals an den Enable-Eingang wird das gated SR-Latch zu einem synchronen Speicherelement, das nur während des hohen Taktsignals auf Eingaben reagiert und den Zustand während des niedrigen Taktsignals beibehält.

Was bedeutet es, dass das gated SR-Latch 'level-sensitive' ist?

-Ein level-sensitives Element wie das gated SR-Latch reagiert auf das Niveau des Taktsignals (hoch oder niedrig) und nicht auf dessen Flanken (steigend oder fallend). Während das Taktsignal hoch ist, reagiert das Latch auf Eingaben; während es niedrig ist, behält es den aktuellen Zustand bei.

Was passiert, wenn sowohl S als auch R im gated SR-Latch gleichzeitig 0 sind?

-Wenn beide Eingänge S und R gleichzeitig 0 sind, behält das gated SR-Latch seinen aktuellen Zustand bei, da keine der beiden Eingaben eine Änderung erzwingt.

Warum ist das gated SR-Latch nicht die bevorzugte Wahl für sequenzielle Schaltungen?

-Das gated SR-Latch ist nicht ideal für sequenzielle Schaltungen, weil es ein level-sensitives Element ist und daher keine präzise Steuerung über die Flanken des Taktsignals bietet. Flip-Flops, die flanksensitiv sind, sind besser für diese Anwendungen geeignet.

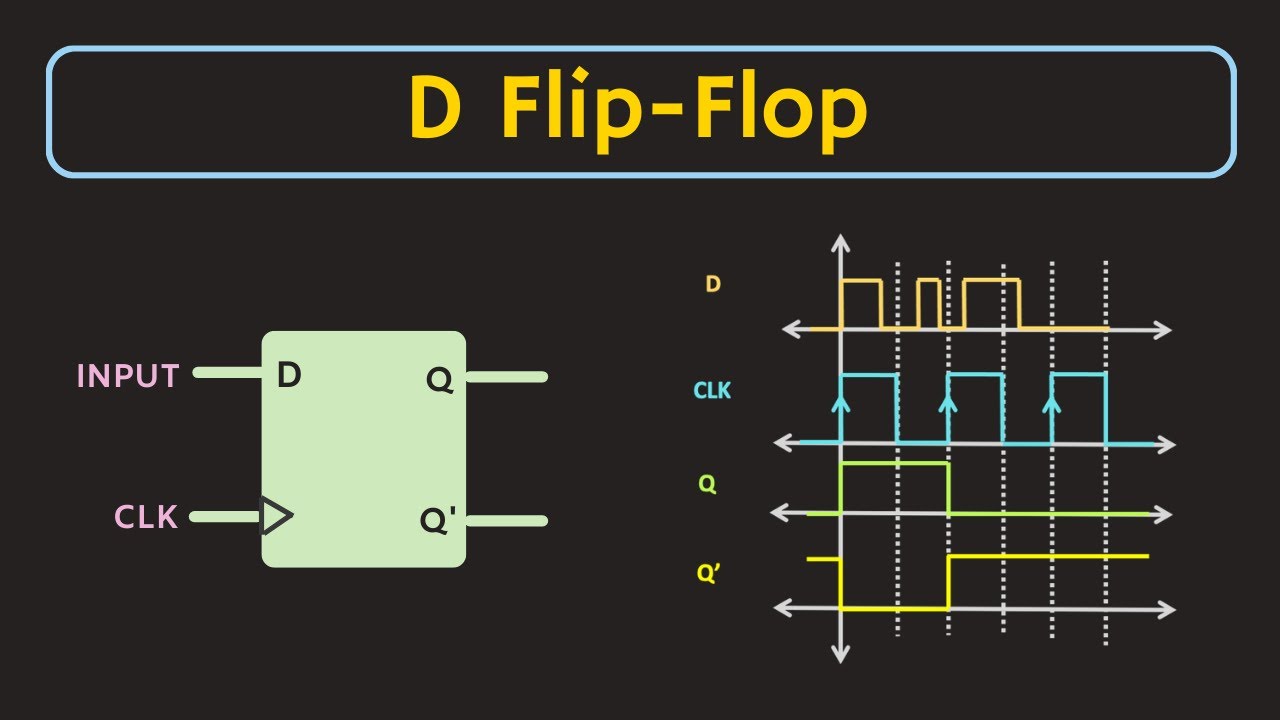

Welche Vorteile bietet ein Flip-Flop im Vergleich zu einem gated SR-Latch in synchronen Schaltungen?

-Ein Flip-Flop ist flanksensensitiv, was bedeutet, dass es nur auf den Übergang des Taktsignals reagiert, anstatt auf das Niveau. Dies ermöglicht eine genauere Synchronisierung und bessere Steuerung in sequenziellen Schaltungen, im Gegensatz zu einem gated SR-Latch, das während eines hohen Taktsignals ständig auf Eingaben reagiert.

Outlines

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифMindmap

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифKeywords

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифHighlights

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифTranscripts

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифПосмотреть больше похожих видео

Latches and Flip-Flops 2 - The Gated SR Latch

Pulse Triggered (Level Triggered or Gated) SR Flip Flop (Latch)

D Flip-Flop Explained | Truth Table and Excitation Table of D Flip-Flop

Surprising bike set up from one of the Top Enduro World Racer

I have nothing for you. SR will 100% reveal what you need.

your luck in life is directly connected to these practices.

5.0 / 5 (0 votes)