Sistem Digital - Flip Flop D, JK dan T

Summary

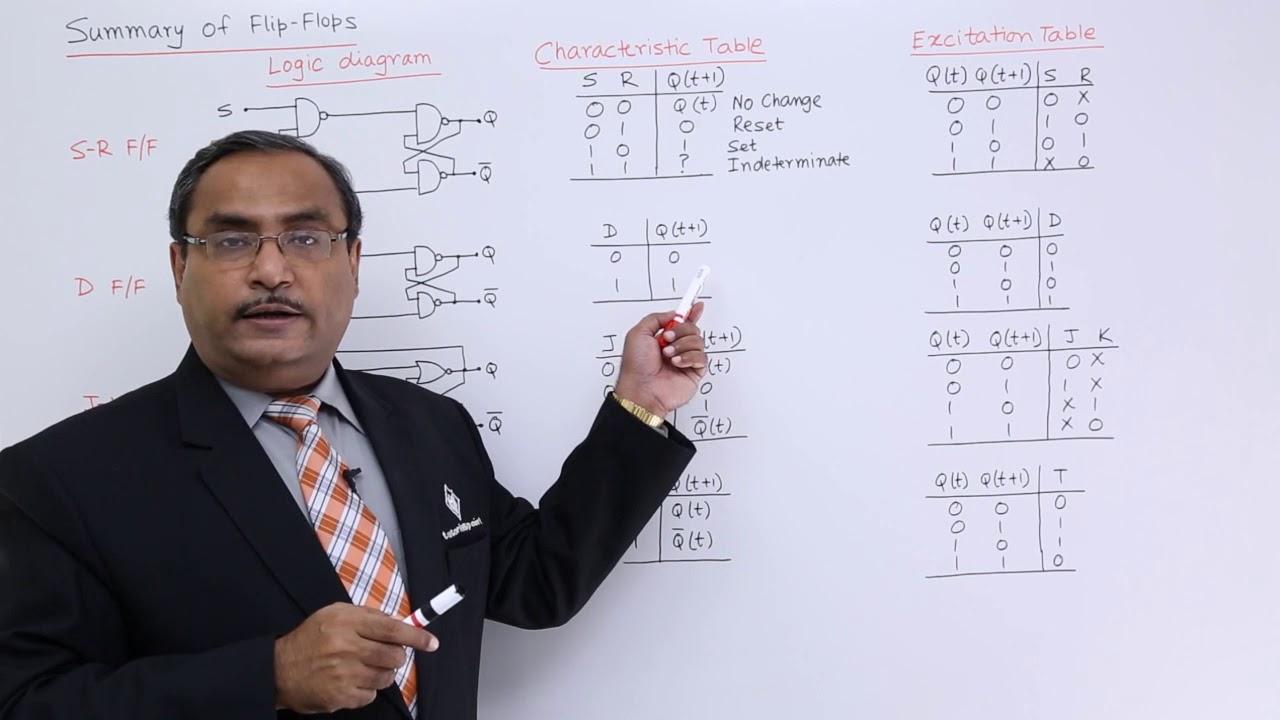

TLDRThis transcript provides a detailed explanation of flip-flops in digital circuits, particularly focusing on SR, D, and JK flip-flops. It covers how these flip-flops function, including their truth tables, behavior with different inputs (such as set, reset, and clock), and methods for avoiding invalid states. The discussion highlights key concepts like output stabilization, data retention, and clock synchronization. Through visual diagrams and logic, the transcript explains the internal mechanics and use cases of these flip-flops in various digital applications, offering insights for learners and practitioners in digital electronics.

Takeaways

- 😀 SR flip-flops are designed to avoid invalid states caused by certain input combinations (like 11).

- 😀 D flip-flops prevent invalid input states by using a single input and a clock signal to maintain stable outputs.

- 😀 The addition of NOT gates can help to correct the SR flip-flop's invalid conditions by ensuring the inputs remain valid.

- 😀 Flip-flops like D flip-flops have specific behaviors based on the clock signal, which controls when outputs change according to inputs.

- 😀 JK flip-flops resolve issues in SR flip-flops by allowing more stable outputs and avoiding invalid states when both inputs are high.

- 😀 The JK flip-flop can toggle between outputs based on inputs, making it more reliable than the SR flip-flop in certain conditions.

- 😀 The use of feedback in JK flip-flops enables more complex operations by allowing outputs to be influenced by previous states.

- 😀 Invalid states, such as both inputs being high (11) in SR flip-flops, are avoided through clever circuit design and logic gates.

- 😀 In flip-flops, the output holds its value even when the clock is inactive, maintaining a stable state until a new clock edge is received.

- 😀 The process of toggling in JK flip-flops allows for the output to switch between states (0 and 1) depending on clock transitions and input conditions.

Q & A

What is the primary advantage of using a D flip-flop over an SR flip-flop?

-The D flip-flop is used to avoid invalid states, particularly the forbidden state of '11' in SR flip-flops, by ensuring stable output transitions.

What happens when the inputs of an SR flip-flop are both set to '1'?

-When both inputs of an SR flip-flop are set to '1', it leads to an invalid state, which is not allowed in typical SR flip-flops. This can be avoided by using a D flip-flop.

How does the addition of a NOT gate to the SR flip-flop affect its operation?

-The NOT gate helps eliminate the invalid input condition '11' by inverting one of the inputs, ensuring that the flip-flop behaves as expected without entering an undefined state.

What is the behavior of the output when a D flip-flop is clocked with a value of '0'?

-When the clock of a D flip-flop is '0', the output holds its previous state, maintaining consistency by not responding to changes in the input.

How does the clock signal influence the output of a flip-flop?

-The clock signal controls the timing of state changes in flip-flops. When the clock transitions (rises or falls), it triggers the flip-flop to update its output based on the current inputs.

What is the significance of the 'JK flip-flop' in the context of avoiding invalid outputs?

-The JK flip-flop avoids invalid outputs by utilizing a feedback mechanism that prevents the undefined '11' input condition found in SR flip-flops, ensuring stable behavior even under such inputs.

What occurs when both inputs of a JK flip-flop are set to '1'?

-When both inputs of a JK flip-flop are set to '1', the output toggles between the previous state and its inverse, rather than entering an invalid state, providing a more reliable operation.

What role does feedback play in the operation of a JK flip-flop?

-Feedback in the JK flip-flop allows the circuit to remember the previous output state, enabling it to toggle between states when both inputs are '1', thus preventing invalid conditions.

How does the JK flip-flop handle input conditions that would typically lead to invalid states in other flip-flops?

-The JK flip-flop handles these conditions by using feedback to toggle the output, instead of entering an invalid state, ensuring that it always produces a valid output.

Why is it important to manage invalid conditions in flip-flops, and how does the script address this issue?

-Invalid conditions in flip-flops can lead to undefined or unstable outputs, which can cause errors in digital systems. The script addresses this by discussing the use of D and JK flip-flops, which prevent invalid states through careful design of input and clock signal handling.

Outlines

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenMindmap

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenKeywords

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenHighlights

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenTranscripts

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenWeitere ähnliche Videos ansehen

FLIP-FLOP - Jenis dan tabel kebenaran

O QUE É O FLIP FLOP? | Como Funcionam os Flip Flops JK, SR, D e T | Eletrônica Digital

Part 5.2 #Latches and #FlipFlops #SequentialCircuits in Digital Electronics in Hindi

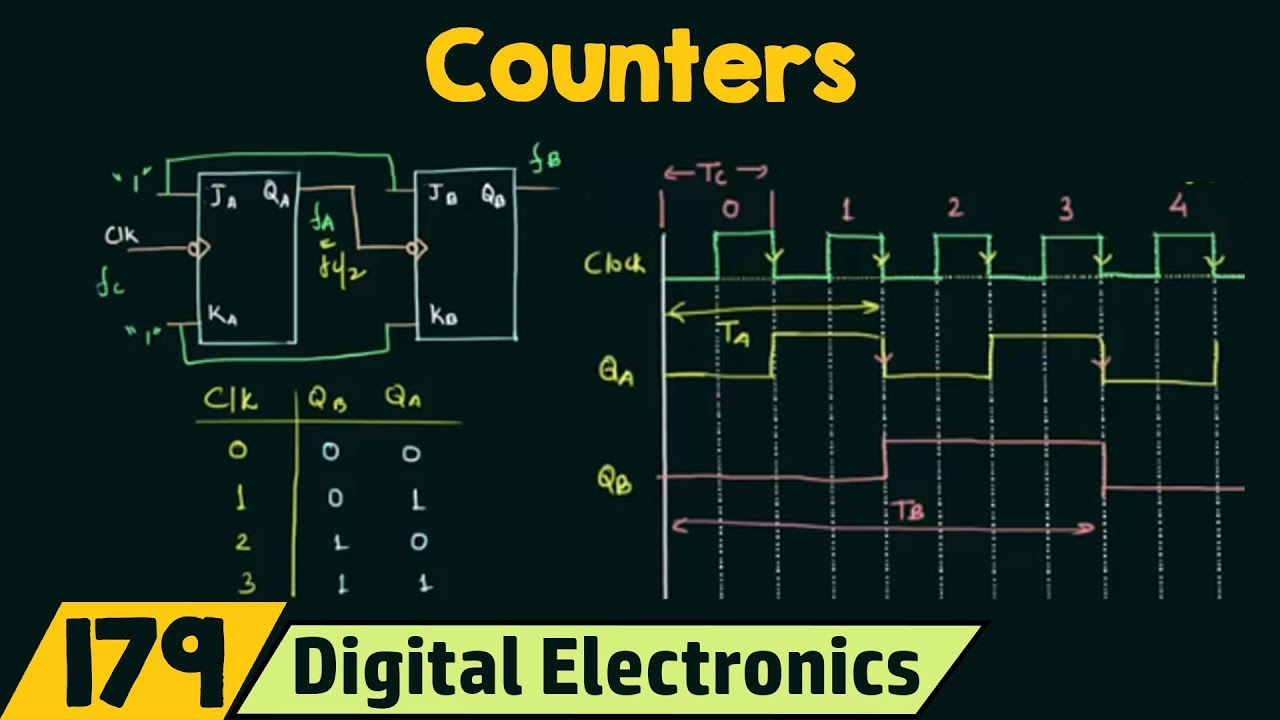

Introduction to Counters | Important

Dasar Sistem Digital | 09 - Register & Counter

Summary of all Flip-Flops

5.0 / 5 (0 votes)