Rangkaian Jam DIgital di EWB (Sistem Digital)

Summary

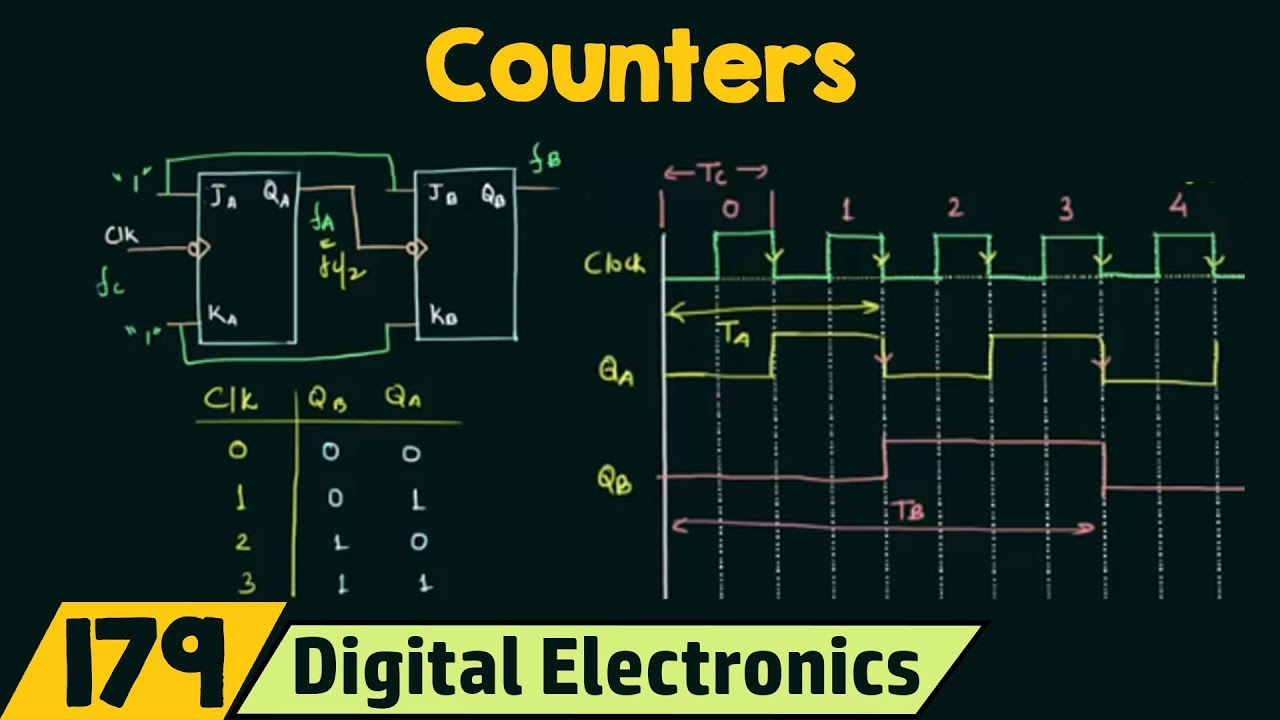

TLDRThis video explains the design and functioning of a digital clock using six seven-segment displays and JK flip-flops. The clock is built with an asynchronous counter, where each flip-flop controls the display of seconds, minutes, and hours. Logic gates are employed to manage counting limits and resets, ensuring proper time progression. The clock operates by counting from 0 to 9 for seconds and minutes, and from 0 to 23 for hours, with resets after reaching the maximum value. This practical demonstration highlights how digital counters and logic gates are used in timekeeping systems.

Takeaways

- 😀 The digital clock circuit uses six JK flip-flops and six seven-segment displays to represent seconds, minutes, and hours.

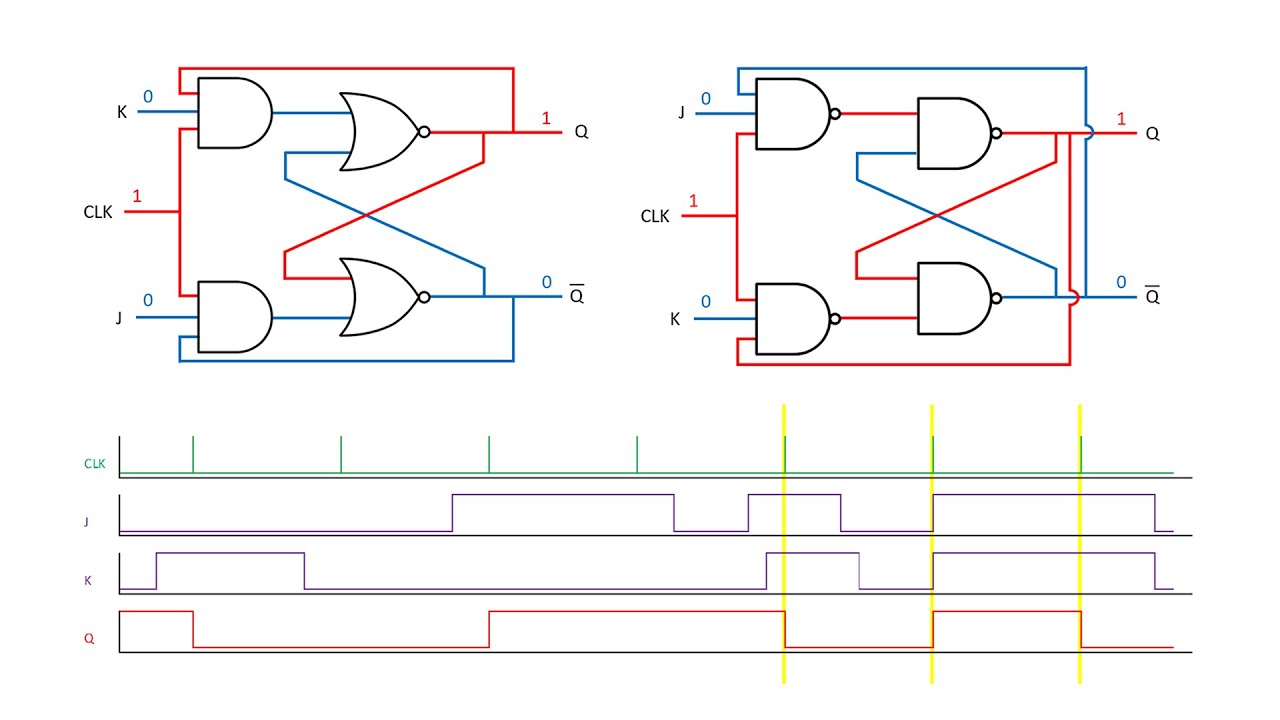

- 😀 Each flip-flop serves as a counter, controlling the counting for seconds, minutes, and hours asynchronously.

- 😀 The circuit uses logic gates (AND, OR, NOT) to limit the counting range of each section (seconds, minutes, and hours).

- 😀 The second section counts from 1 to 9, and after reaching 10, it resets to 0.

- 😀 The minute section counts from 1 to 5 and resets after reaching 6, limiting the count to 5.

- 😀 The hour section counts from 0 to 23, and when the hour reaches 24, it resets to 0.

- 😀 The counters are asynchronous because each flip-flop's output serves as the input for the next flip-flop in the sequence.

- 😀 Each section of the clock (seconds, minutes, hours) is controlled by specific reset logic to start counting again after reaching a limit.

- 😀 The seven-segment displays are controlled by binary numbers, where the inputs determine the segments that are lit to show the numbers.

- 😀 The clock operates with a frequency of 11 Hz, driving the timing of the count and updates on the display.

- 😀 The clock system ensures accurate timekeeping by using resets after each segment reaches its limit (e.g., after 9 seconds, 59 minutes, or 23 hours).

Q & A

What is the purpose of the circuit described in the script?

-The purpose of the circuit is to create a digital clock that displays time using six seven-segment displays and JK flip-flops to count and show seconds, minutes, and hours.

How many JK flip-flops are used in the circuit?

-Six JK flip-flops are used in the circuit, with each flip-flop responsible for counting a specific part of the time (seconds, minutes, or hours).

What does each seven-segment display represent in the circuit?

-Each seven-segment display is used to show a part of the time: two displays show seconds (one unit and tens), two display minutes (one unit and tens), and two display hours (one unit and tens).

What type of counter is used in this digital clock design?

-An asynchronous counter is used, meaning that the input for each flip-flop comes from the output of the previous flip-flop, creating a sequential counting mechanism.

Why is the counter considered asynchronous?

-The counter is asynchronous because each flip-flop’s input is driven by the output of the previous flip-flop, instead of all flip-flops being synchronized with a single clock signal.

How does the circuit prevent the seconds unit from counting beyond 9?

-The circuit uses an AND gate to limit the count of the seconds unit. Once it reaches 10, the counter resets to 0, ensuring it only counts from 0 to 9.

What is the purpose of the logic gates in the circuit?

-The logic gates (AND and OR gates) are used to control the reset behavior of the flip-flops. They limit the count, such as resetting the counter once it reaches a specific value (e.g., 10 for seconds or 6 for minutes).

How does the circuit manage the minutes and hours counting?

-Similar to the seconds unit, the minutes and hours are also controlled by logic gates. For minutes, the count resets at 10, and for hours, it resets at 24 to maintain correct time display.

What happens when the hour counter reaches 24?

-Once the hour counter reaches 24, the counter resets back to 0, ensuring the time cycles correctly from 00:00 to 23:59.

What frequency is used for the clock signal in the circuit?

-The clock signal in the circuit has a frequency of 11 Hz, which drives the counting process of the flip-flops.

Outlines

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenMindmap

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenKeywords

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenHighlights

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenTranscripts

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenWeitere ähnliche Videos ansehen

5.0 / 5 (0 votes)