How double data rate DRAM works

Summary

TLDR在本视频中,Bill Zoid 讲解了 DDR(双倍数据速率)如何实现的原理,重点分析了 DDR4 的写操作和读操作的时序图。通过对比写操作和读操作,他阐明了内存控制器在数据对齐和同步中的关键角色,尤其是在如何通过调整数据电压和时钟边缘来实现双倍数据速率的过程。视频内容深入浅出,帮助观众理解复杂的内存数据传输机制,尤其适合对计算机硬件有兴趣的观众。

Takeaways

- 😀 DDR(双倍数据速率)通过时钟边缘传输数据,而不仅仅是简单的在时钟边缘传输数据。

- 😀 通过对DDR4的写突发操作(write burst operation)和读突发操作(read burst operation)进行分析,揭示了DDR如何实现双倍数据速率。

- 😀 写突发操作开始时,内存控制器发送写命令,内存芯片开始准备接收数据。

- 😀 DDR使用差分时钟信号,这意味着它有两个版本的信号——正向和负向。每个时钟周期包括两个时钟边缘(上升沿和下降沿)。

- 😀 写预导(write preamble)是用来确保数据传输开始前数据队列时钟(DQ Strobe)已启动,防止数据丢失。

- 😀 数据队列(Data Queue)是通过单端连接传输数据,每个数据队列同时传输一个比特的数值,内存芯片通常有多个数据队列。

- 😀 数据传输过程中,内存控制器会调整数据与时钟的相对对齐,以确保内存芯片能准确读取数据。

- 😀 在写操作中,内存控制器负责先行调整数据的电压,以确保内存芯片在时钟边缘采样到正确的数据值。

- 😀 在读操作中,内存芯片通过时钟边缘触发数据变化,而内存控制器使用一个与时钟信号相位错开的时钟信号(读取时钟)来正确采样数据。

- 😀 双倍数据速率的实现基于内存控制器的精密操作,通过使数据在时钟边缘前后适当对齐,从而实现每个时钟周期两次有效的数据传输。

- 😀 DDR的高效性部分源自内存控制器复杂的时序和数据对齐机制,使得即便内存芯片本身结构简单,也能实现高效的双倍数据速率。

Q & A

什么是DDR内存,它是如何工作的?

-DDR(双倍数据速率)内存通过在时钟周期的上升和下降沿传输数据,从而实现数据传输速度的加倍。它利用时钟信号的两个边缘来传输数据,而不仅仅是一个时钟边缘。

什么是DDR4和DDR5中的‘银行组’?

-银行组(Bank Group)是DDR4和DDR5内存中的一个特性,用来提高内存访问的效率。它将内存划分为多个组,使得不同的数据可以在同一时间被访问,从而减少延迟并提高带宽。

如何理解DDR内存中的‘数据队列’(Data Queue)?

-数据队列(Data Queue)是从内存控制器到内存芯片的数据传输通道。在DDR4和DDR5中,每个内存芯片有多个数据队列,每个队列负责传输一位数据。这些队列是并行工作的,能够同时传输多个数据位。

为什么DDR内存使用差分时钟信号?

-DDR内存使用差分时钟信号,因为这种信号通过正负两条信号线传输数据,从而提高信号的稳定性,减少噪声干扰,保证数据的可靠性。

‘写预置’(Write Preamble)在DDR内存操作中起什么作用?

-‘写预置’(Write Preamble)是内存控制器在开始数据传输之前启动数据队列时钟信号的延时。这确保在开始数据传输前,数据队列的时钟信号已经处于稳定状态,防止数据丢失或传输错误。

DDR内存是如何在‘写突发操作’(Write Burst Operation)中进行数据传输的?

-在‘写突发操作’中,内存控制器会通过调整数据队列的电压水平,在时钟边缘之前发送数据。内存芯片在每个时钟周期的上升或下降沿采样数据,完成双倍数据率的传输。

为什么内存控制器需要在时钟边缘前调整数据电压?

-内存芯片的工作方式决定了它只能在时钟边缘采样数据,因此为了保证数据正确传输,内存控制器必须在时钟边缘前调整数据电压,以确保数据在采样时处于正确的状态。

‘读取操作’(Read Operation)和‘写入操作’(Write Operation)在DDR内存中有何不同?

-在‘读取操作’中,内存芯片会在时钟边缘改变数据电压,而内存控制器需要通过一个90度相位差的读取时钟来正确采样数据。而在‘写入操作’中,内存控制器在时钟边缘前调整数据电压,内存芯片则在时钟边缘采样数据。

什么是‘读取时钟’(Read Clock)?它如何在DDR内存中工作?

-‘读取时钟’是内存控制器中用于读取数据的第二时钟信号,它相对于主时钟有90度的相位差。它帮助内存控制器正确采样内存芯片在时钟边缘输出的电压数据。

如何实现双倍数据率(DDR),它依赖于哪些关键操作?

-实现双倍数据率的关键在于内存控制器的操作。在写操作中,内存控制器通过调整数据电压的时机,使得内存芯片能够在每个时钟周期的两个时钟边缘采样数据。在读操作中,内存控制器通过90度相位差的读取时钟采样内存芯片的输出数据,从而实现每个时钟周期两次数据传输。

Outlines

此内容仅限付费用户访问。 请升级后访问。

立即升级Mindmap

此内容仅限付费用户访问。 请升级后访问。

立即升级Keywords

此内容仅限付费用户访问。 请升级后访问。

立即升级Highlights

此内容仅限付费用户访问。 请升级后访问。

立即升级Transcripts

此内容仅限付费用户访问。 请升级后访问。

立即升级浏览更多相关视频

Hash table hash function

Add a ViewModel with @EnvironmentObject in SwiftUI | Todo List #3

【牛市必杀技!】马丁回归策略,3.0飞升版本的仓位管理策略,来自DC的很邪恶的交易方法 #交易策略 #martingale #okx

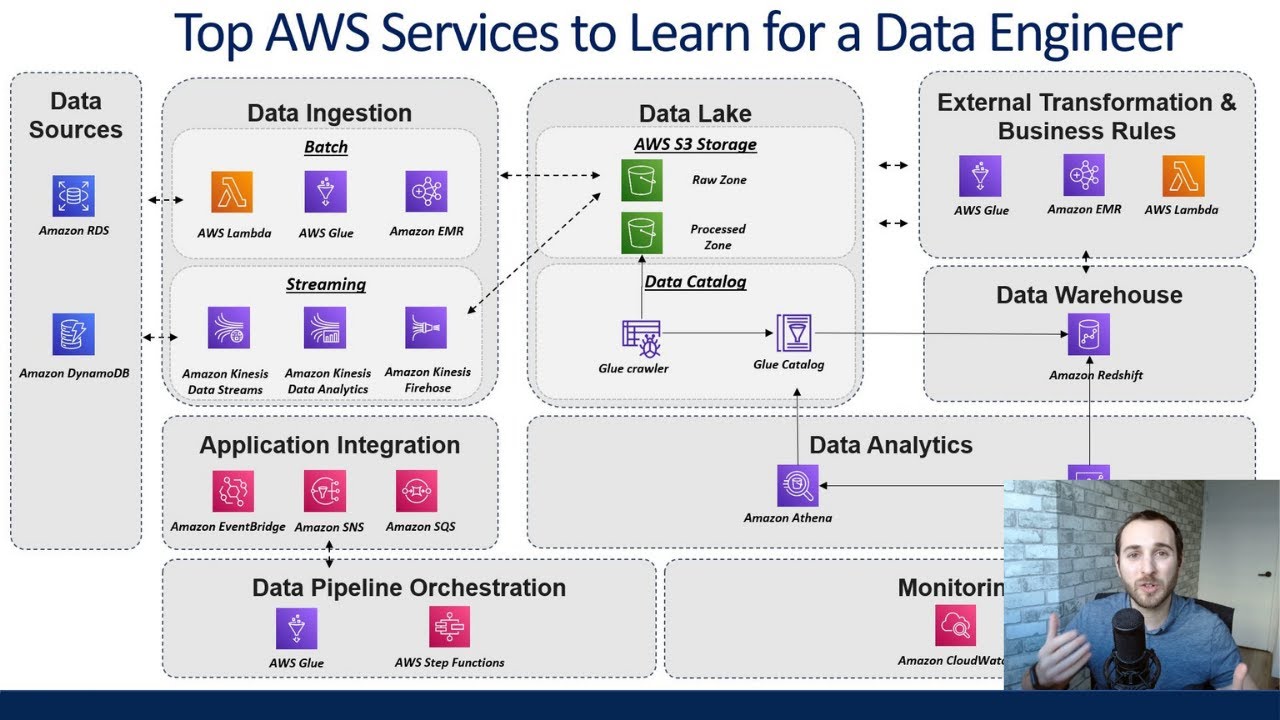

Top AWS Services A Data Engineer Should Know

CCIR - Quantum Physics: Information, Foundations And Gravity - Lecture Session #1

RVC, Style-Bert-Vits2, VCclientのつかいかた【AI音声生成】

5.0 / 5 (0 votes)