Clocked SR Flip Flop using NAND Gates with Truth Table and Circuit Diagram

Summary

TLDRThis video tutorial explains the concept and working of the clocked SR flip flop in digital electronics. It begins by reviewing the basic SR flip flop and then introduces the clocked version, highlighting the role of the clock signal in synchronizing output changes. The tutorial walks through a detailed analysis of the truth table across five key cases: memory state, reset state, set state, latched state, and race condition. It concludes by emphasizing how the clock helps prevent undesirable outputs and provides greater control over flip flop behavior, ensuring reliable digital circuit performance.

Takeaways

- 😀 Clocked SR flip-flop is an enhanced version of the basic SR flip-flop, which includes a clock input for better control and synchronization.

- 😀 The primary function of the clocked SR flip-flop is to control the output based on the clock signal, avoiding undesired changes when the clock is off.

- 😀 When the clock signal (CLK) is 0, the SR flip-flop behaves as a memory latch, retaining the previous state (Qn-1, Qn-1').

- 😀 The addition of the clock input makes the SR flip-flop more stable by preventing changes in output when CLK is 0, even if the inputs S and R are toggled.

- 😀 With the clock set to 1, the SR flip-flop is active, and the outputs depend on the inputs S and R, allowing the flip-flop to switch between set and reset states.

- 😀 In case the clock is 1, when S=0 and R=1, the flip-flop will reset to Q=0 and Q'=1, which is the reset state.

- 😀 When S=1 and R=0, with the clock still at 1, the flip-flop sets the state to Q=1 and Q'=0, which is the set state.

- 😀 If both S and R are 0 while CLK is 1, the SR flip-flop maintains its previous state, a behavior known as 'memory state'.

- 😀 When both S and R are 1 with the clock at 1, the flip-flop enters a 'race condition', which results in an undesirable output where Q equals Q'.

- 😀 The race condition can be avoided by ensuring that the clock remains 0 when S and R are both 1, thereby forcing the flip-flop to maintain its previous state and prevent any contradictory outputs.

Q & A

What is the main topic discussed in the video?

-The main topic discussed in the video is the concept and working of the clocked SR (Set-Reset) flip-flop, a modified version of the basic SR flip-flop with an added clock input for synchronization and control.

What is the purpose of adding a clock signal to the SR flip-flop?

-The clock signal is added to synchronize the flip-flop's operation, allowing the output to be controlled. When the clock is off (0), the flip-flop retains its previous state, and when the clock is on (1), the output depends on the inputs S and R.

How does the clocked SR flip-flop behave when the clock is 0?

-When the clock is 0, the clocked SR flip-flop functions as a memory latch. Regardless of the values of the S and R inputs, the output remains the same as the previous state, meaning the flip-flop does not change.

What happens when the clock is 1 and S = 0, R = 1?

-When the clock is 1 and S = 0, R = 1, the flip-flop is reset. The output Q becomes 0, and Q-bar becomes 1, resetting the flip-flop.

What is the behavior of the clocked SR flip-flop when S = 1 and R = 0?

-When the clock is 1 and S = 1, R = 0, the flip-flop is set. The output Q becomes 1, and Q-bar becomes 0, setting the flip-flop.

What happens if both S and R are 0 while the clock is 1?

-If both S and R are 0 while the clock is 1, the flip-flop retains its previous state, which means the output Q and Q-bar stay the same as the last values, maintaining memory.

What is the race condition in a clocked SR flip-flop?

-The race condition occurs when both S and R are 1 while the clock is 1. This creates an undesirable output because Q and Q-bar cannot both be 1, leading to an undefined state. This is called a race condition, which is an undesirable behavior.

How does the clock prevent a race condition in the SR flip-flop?

-The clock prevents a race condition by disabling the flip-flop when it is 0. If the clock is 0, the inputs S and R do not affect the output, which stays in the previous state, thus avoiding the race condition.

What does the truth table for the clocked SR flip-flop show when the clock is 0?

-When the clock is 0, the truth table shows that the output is always the previous state, regardless of the values of S and R. The flip-flop essentially acts as a memory latch, keeping the previous output values (Q = Q_n-1, Q-bar = Q_bar_n-1).

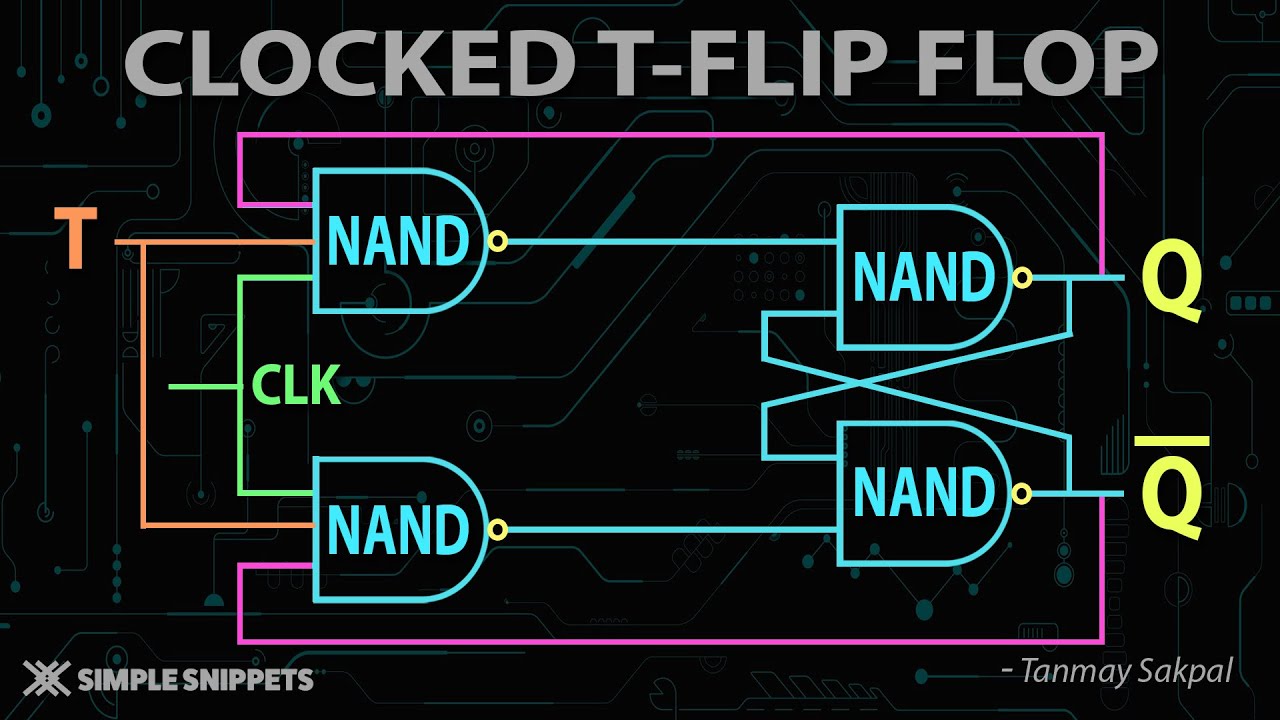

What role do NAND gates play in the clocked SR flip-flop?

-NAND gates are used in both the clocked SR flip-flop and its basic version. They perform the logic operations for the Set and Reset actions, as well as maintaining the memory state by providing feedback between the Q and Q-bar outputs.

Outlines

此内容仅限付费用户访问。 请升级后访问。

立即升级Mindmap

此内容仅限付费用户访问。 请升级后访问。

立即升级Keywords

此内容仅限付费用户访问。 请升级后访问。

立即升级Highlights

此内容仅限付费用户访问。 请升级后访问。

立即升级Transcripts

此内容仅限付费用户访问。 请升级后访问。

立即升级浏览更多相关视频

Clocked T Flip Flop using NAND Gates with Truth Table and Circuit Diagram

FLIP-FLOP - Jenis dan tabel kebenaran

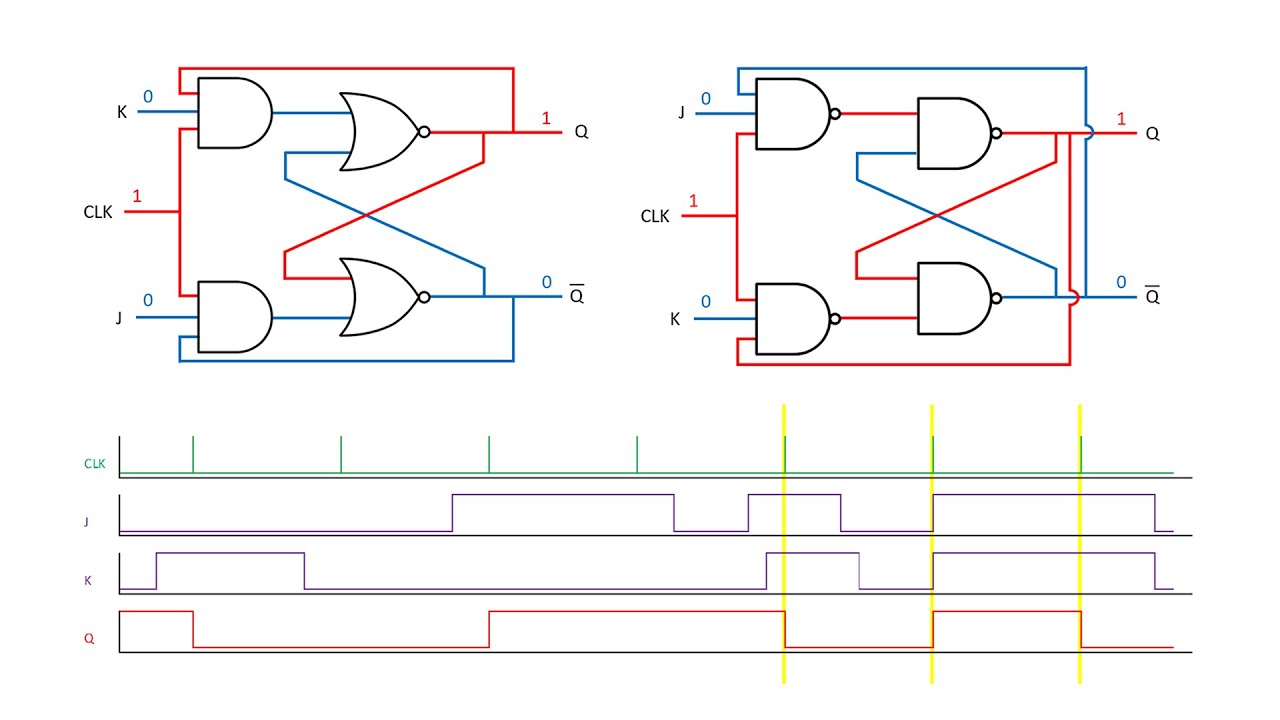

Latches and Flip-Flops 6 - The JK Flip Flop

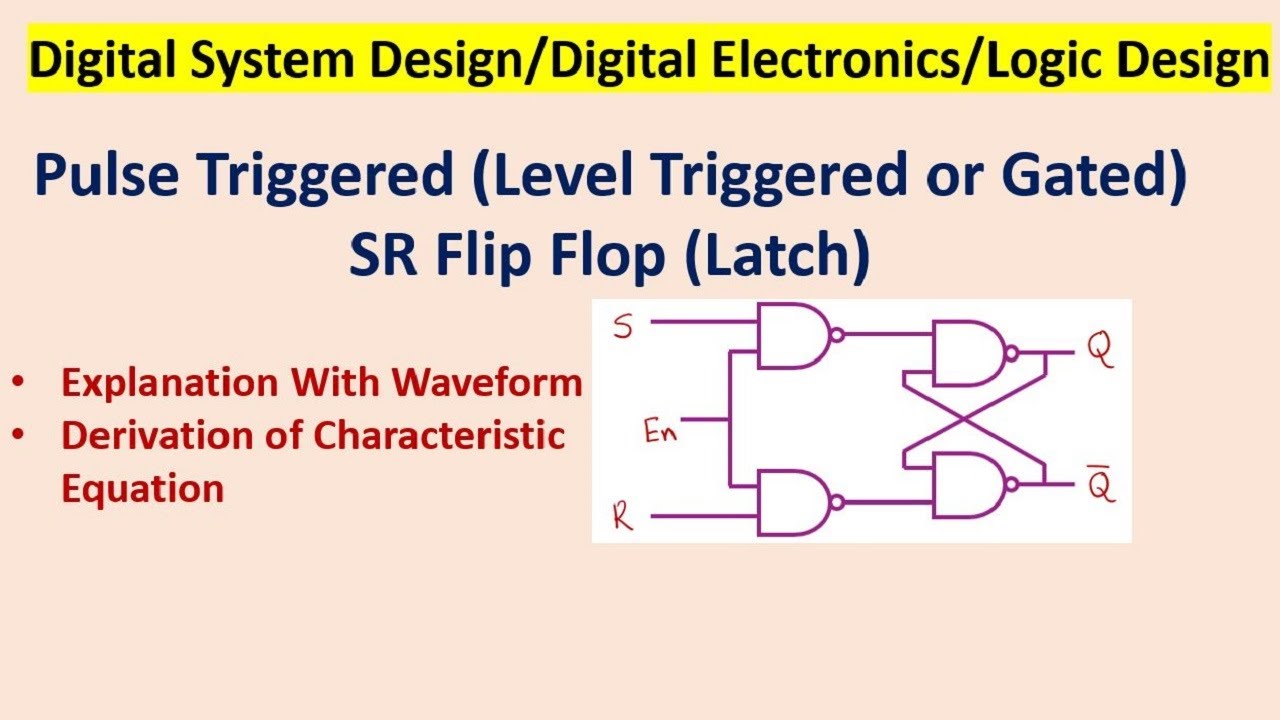

Pulse Triggered (Level Triggered or Gated) SR Flip Flop (Latch)

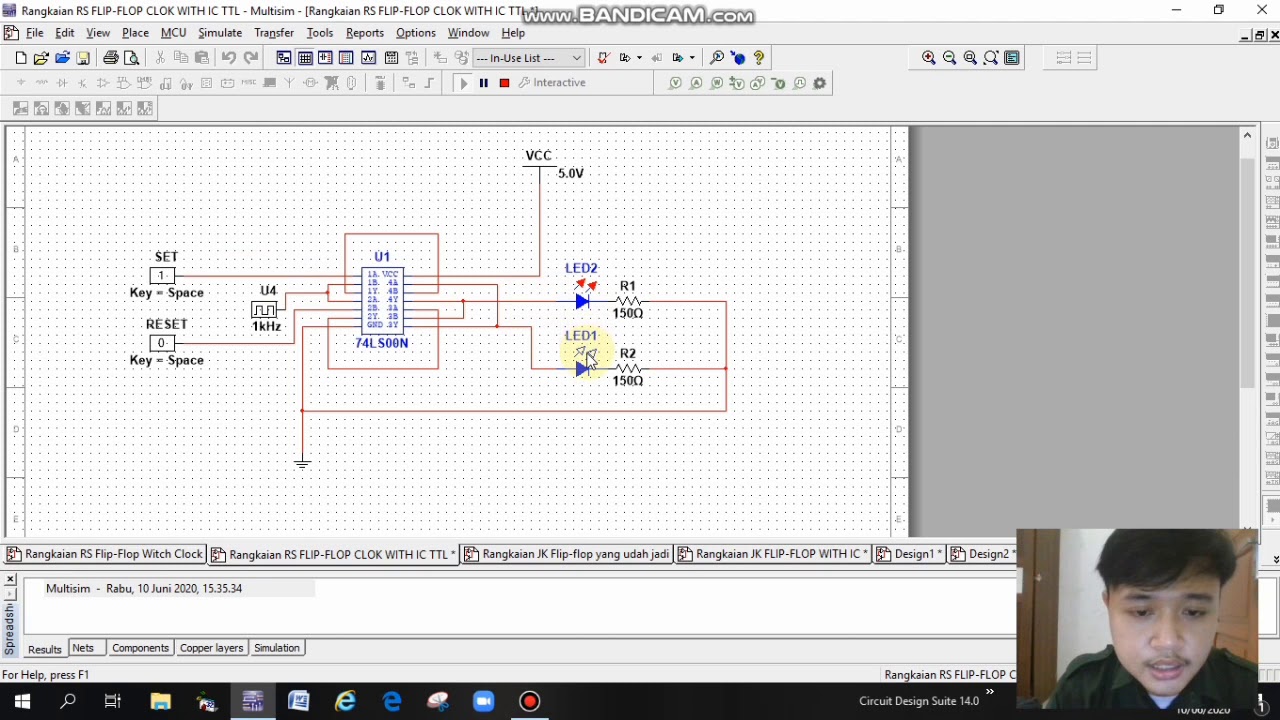

Simulasi Rangkaian JK Flip-flop, RS Flip-flop, dan D Flip-flop ( Faishal Satria G 2211181006 )

Part 5.2 #Latches and #FlipFlops #SequentialCircuits in Digital Electronics in Hindi

5.0 / 5 (0 votes)