How to create a signal vector in VHDL: std_logic_vector

Summary

TLDRIn this tutorial, Jonas from VHDL is Calm introduces the 'standard logic vector' type in VHDL, ideal for representing collections of signals. He demonstrates how to declare and initialize vectors, including setting initial values to zero, one, or specific hexadecimal and binary values. Jonas also explains the significance of 'downto' in vector declaration and shows how to iterate over vector bits, creating a shift register example. The tutorial emphasizes the use of attributes for more generic and adaptable code, encouraging hands-on learning for mastering VHDL.

Takeaways

- 😀 The video is a tutorial on using the standard logic vector type in VHDL, which is an array version of the standard logic type.

- 🔍 The standard logic vector is used to represent a collection of wires, such as a byte-wide data bus.

- 📝 To declare a signal of type standard logic vector, specify the size with a range, for example, '7 downto 0' for an 8-bit vector.

- 💡 Uninitialized vectors in VHDL are shown as 'X' in the simulator, indicating an unknown state.

- 🟢 Signals can be initialized to specific values using syntax like 'others => '0'' for all bits set to zero.

- 🔢 The tutorial demonstrates how to give initial values to vectors in different formats, including binary and hexadecimal.

- 🔄 The 'downto' keyword is a VHDL convention for specifying the direction of a vector's index, but it can also be reversed with 'to'.

- 🚫 Attempting to use 'to' incorrectly results in a compilation error, highlighting the importance of proper syntax.

- 🔁 The video shows how to create a shift register by iterating over bits in a standard logic vector and using a feedback loop.

- 🔑 Using attributes like 'left' and 'right' for indexing is preferred over hardcoding values, making the code more adaptable.

- 📚 The tutorial concludes by encouraging viewers to practice VHDL themselves and to explore the provided resources for further learning.

Q & A

What is the main topic of this tutorial?

-The main topic of this tutorial is how to use the standard logic vector type in VHDL.

What is a standard logic vector type in VHDL?

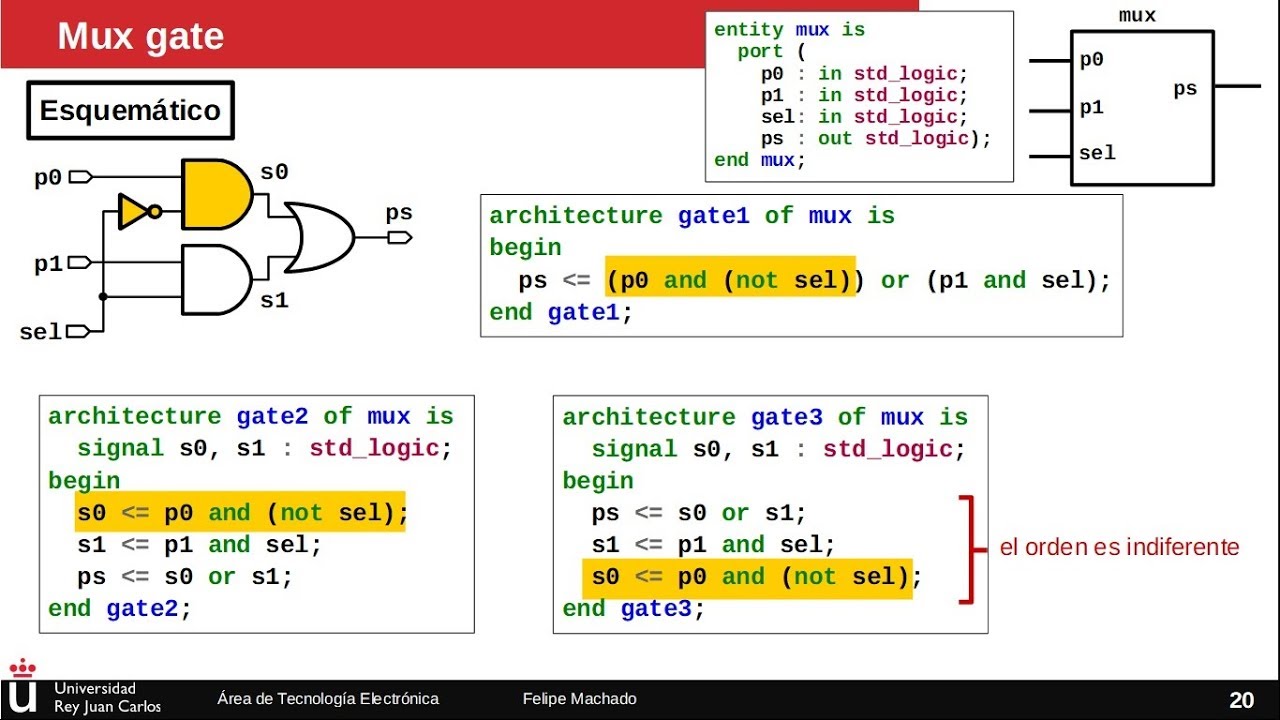

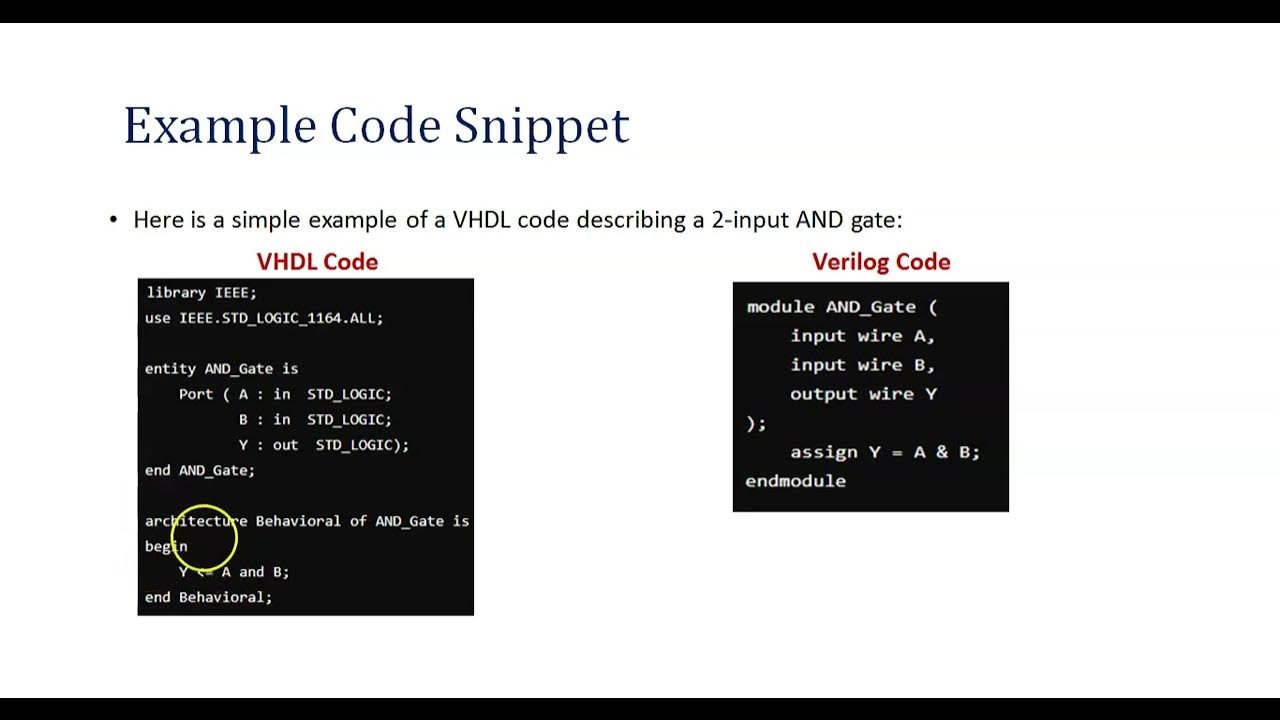

-A standard logic vector type in VHDL is an array version of the standard logic type, used for describing a collection of values that can be carried by multiple wires.

How is a standard logic vector declared in VHDL?

-A standard logic vector is declared by specifying the type as 'STD_LOGIC_VECTOR' followed by the size of the vector in parentheses, indicating the range from the highest index down to the lowest.

What is the preferred way to declare an 8-bit vector in VHDL?

-The preferred way to declare an 8-bit vector in VHDL is by specifying the range from 7 down to 0, as this includes all 8 bits.

What does the uninitialized value 'X' in a waveform represent?

-In a waveform, the uninitialized value 'X' represents an unknown or undefined state, indicating that the signal has not been initialized.

How can you give an initial value to a standard logic vector?

-You can give an initial value to a standard logic vector by using the ':=' operator followed by the value in a format like '(others => '0')' for all zeros, or '(others => '1')' for all ones.

What is the difference between using 'downto' and 'to' in the range of a vector declaration?

-Using 'downto' specifies the range from a higher index to a lower index, while 'to' specifies the range from a lower index to a higher index. The direction of the range affects the indexing of the bits.

How can you represent the initial value of a standard logic vector in hexadecimal?

-The initial value of a standard logic vector can be represented in hexadecimal by using the notation 'x"' followed by the hexadecimal value in double quotation marks.

What is a shift register and how is it created in VHDL?

-A shift register is a type of digital circuit that shifts the bits of its input in a specific direction, typically left or right. In VHDL, it can be created by iterating over the bits in a standard logic vector and shifting them, while also providing feedback to maintain the bit pattern.

Why is it recommended to use attributes for indexing in VHDL?

-Using attributes for indexing in VHDL is recommended because it makes the code more generic and adaptable to changes in the signal's bit width. Attributes like 'LEFT' and 'RIGHT' provide dynamic indexing that adjusts automatically based on the vector size.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

5.0 / 5 (0 votes)