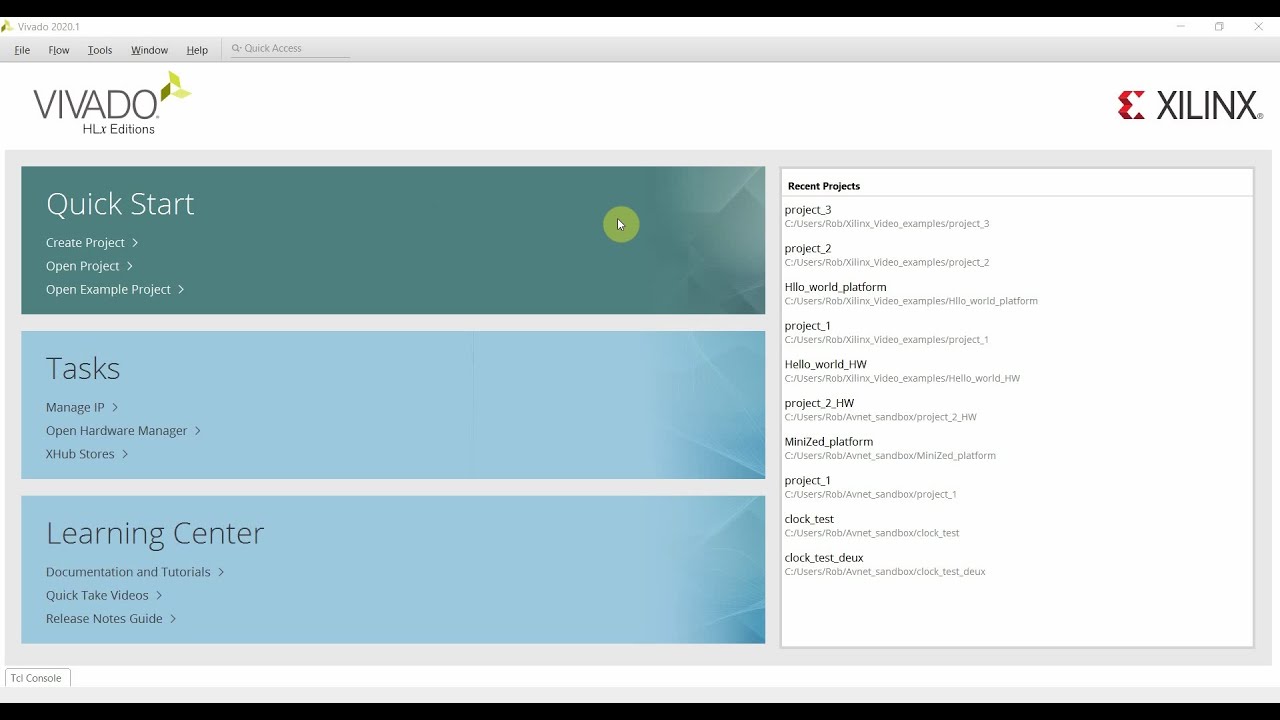

Vivado01 1 Familiarizacao com o Vivado e Simulacao de uma AND2

Summary

TLDRIn this tutorial, the presenter walks viewers through the process of creating a simple VHDL program using Vivado, a software suite for FPGA design. The video demonstrates how to set up a project in Vivado, select the appropriate hardware components, and write basic VHDL code for a simple AND gate with two inputs and one output. The presenter also covers how to simulate the design using Vivado’s built-in simulator to visualize the logic behavior. This tutorial is aimed at beginners seeking to familiarize themselves with VHDL and FPGA simulation in a straightforward, hands-on manner.

Takeaways

- 😀 Start by creating a new project in Vivado, specifying the chip and project type (RTL) for your design.

- 😀 Choose the correct version of Vivado and set the project path to keep everything organized.

- 😀 The VHDL design requires defining input and output ports, such as two inputs (A and B) and one output (S) for a simple AND gate.

- 😀 Use Vivado's built-in wizard to assist with project setup and creating the necessary VHDL files.

- 😀 When naming files and projects in Vivado, avoid spaces or special characters, and ensure names are unique to prevent conflicts.

- 😀 VHDL requires importing libraries, such as 'std_logic_1164', which provide essential functions for logic operations.

- 😀 In the VHDL code, define the behavior of the AND gate using simple statements like 'S <= A AND B' within the architecture section.

- 😀 Save your VHDL files frequently to avoid issues, as unsaved work can lead to errors or lost progress.

- 😀 After creating the design, simulate it using Vivado’s built-in simulator to check if the logic works as expected.

- 😀 Set input values (e.g., 0 and 1) and verify that the output (S) behaves as an AND gate: 0 AND 0 = 0, 1 AND 0 = 0, 1 AND 1 = 1.

- 😀 For more complex simulations, consider using testbenches to simulate circuit behavior more accurately, but for simple designs, Vivado’s basic simulator is sufficient.

Q & A

What is the main purpose of the video tutorial?

-The main purpose of the video is to provide a basic introduction to using Vivado for creating a simple project with VHDL, including basic simulation and familiarization with the Vivado interface.

Which version of Vivado is being used in the tutorial?

-The tutorial uses Vivado version 2009.2.

What is VHDL, and why is it used in this tutorial?

-VHDL (VHSIC Hardware Description Language) is a language used for describing the behavior and structure of electronic systems. In this tutorial, VHDL is used to write the design code for simulating a simple AND gate circuit.

How does the tutor start the process of creating a project in Vivado?

-The tutor starts by creating a new project using Vivado's wizard. The project is named, and a directory path is chosen for saving the project files.

What is the 'RTL project' option used for in Vivado?

-The 'RTL project' option in Vivado is selected when creating projects that involve Register Transfer Level design, which is commonly used in FPGA and hardware simulation. This option is used to build and simulate hardware designs like the one in the tutorial.

How does the tutor select the chip or FPGA for the project?

-The tutor selects the chip by searching for it in Vivado's device settings, either by choosing a predefined option or manually finding the exact chip from the project specifications, using the manual if necessary.

What is the purpose of selecting a source file type in Vivado?

-Selecting a source file type in Vivado defines the kind of code or design files being used. In the tutorial, VHDL is chosen as the source file type for creating a hardware description for the AND gate.

What does the tutor demonstrate in the process of writing the VHDL code?

-The tutor demonstrates how to write the VHDL code for a simple AND gate with two input ports and one output port. The inputs and outputs are defined, and basic operations like specifying bit lengths and connections are shown.

Why is saving the project files regularly emphasized in the video?

-Saving the project files regularly is emphasized to avoid losing changes or encountering errors that might occur if files are not saved. The tutor highlights this as a common mistake that can affect the simulation or implementation of the project.

What simulation method does the tutor use for testing the VHDL code?

-The tutor uses Vivado's built-in simulator for testing the VHDL code. This method is suitable for simple circuits like the AND gate, as it allows for visualization of input-output behavior without needing a more complex external testbench.

What steps does the tutor take to perform a simulation of the AND gate circuit?

-To perform the simulation, the tutor initializes the simulation environment, sets up the input values for the AND gate, and runs the simulation to observe the output behavior. The results are visualized on a waveform chart to confirm the correct logic operation.

What are some challenges mentioned by the tutor when simulating more complex circuits?

-The tutor mentions that Vivado's built-in simulator is only suitable for simple circuits. For more complex simulations, a more detailed testbench and external simulation tools would be necessary.

What future steps does the tutor mention for completing the project?

-In future videos, the tutor plans to show how to implement the VHDL design on an actual FPGA (specifically the B6 chip) and how to handle additional project details like file organization and managing hardware constraints.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

Design, Implement, and Visualize: XADC IP for FPGA Temperature Monitoring in Vivado

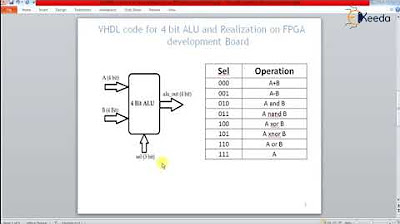

VHDL code for 4 bit ALU and Realization on FPGA development Board

Hello world video using Xilinx Zynq, Vivado 2020, and Vitis

VHDL Lecture 4 Lab1-Switches LEDs Simulation

How to Download and Install Xilinx ISE Design Suite on Windows 10 & 11 (Step-by-Step Guide)

CARA MEMBUAT PINTU DI SKETCHUP - GAMPANG BANGET

5.0 / 5 (0 votes)