SAYISAL ELEKTRONİK DERSLERİ: JK Flip Flop

Summary

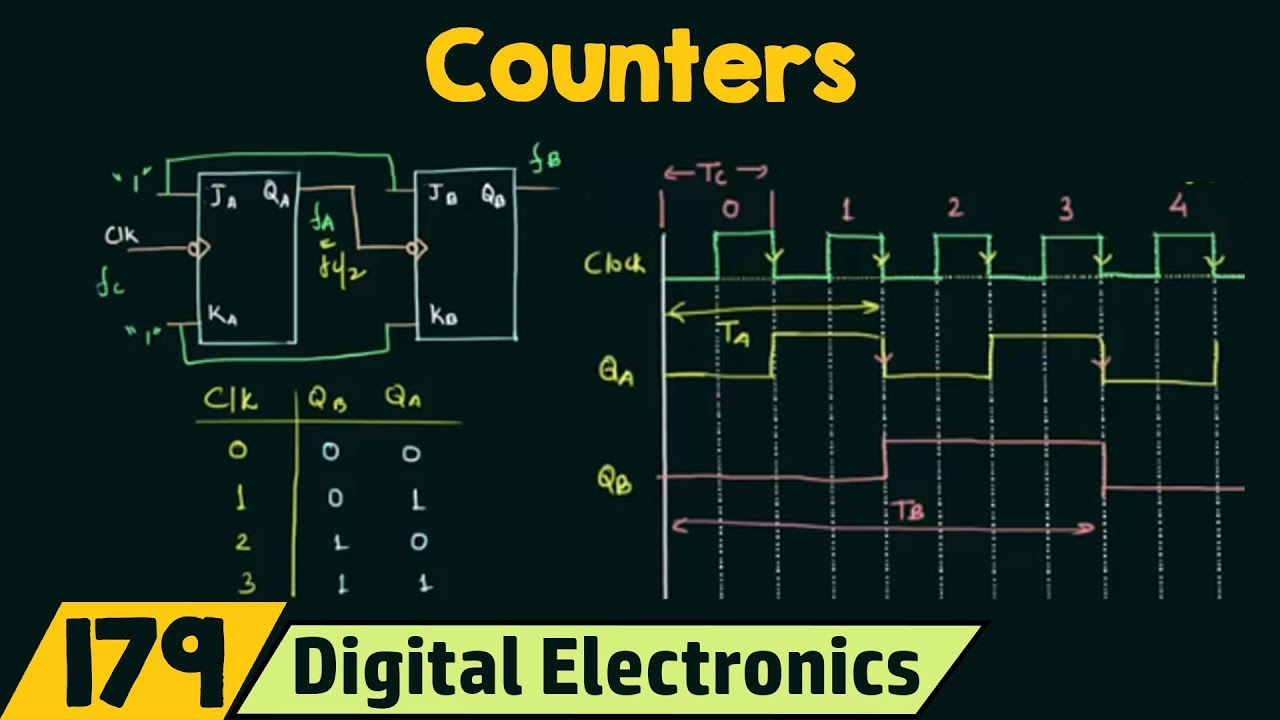

TLDRIn this tutorial, the presenter explains the functionality of JK flip-flops, highlighting their similarities and differences compared to RS flip-flops. The video covers the circuit diagram, truth table, and key characteristics of the JK flip-flop, including how it handles various input conditions. The presenter demonstrates the process of building and simulating a JK flip-flop circuit, troubleshooting issues, and exploring the behavior of the flip-flop through practical examples. Emphasis is placed on the role of preset and clear inputs, and how they affect the output, providing a comprehensive guide to understanding and simulating JK flip-flops.

Takeaways

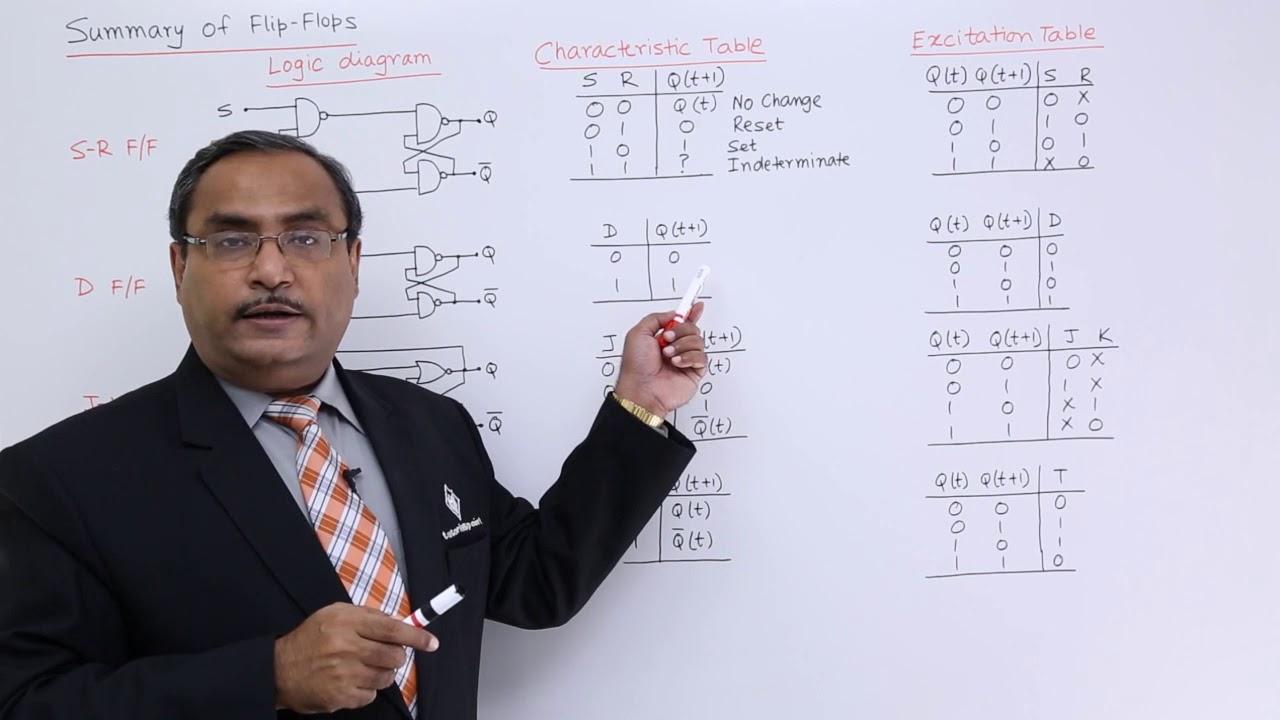

- 😀 JK flip-flops have two inputs (J and K) and a clock input, which differentiates them from RS flip-flops, which have Set and Reset inputs.

- 😀 The JK flip-flop's behavior depends on its inputs (J and K) and clock signal. For example, J=0 and K=1 will set Q to 1, and J=1 and K=0 will reset Q to 0.

- 😀 When both J and K are 1, the JK flip-flop toggles its state, meaning the output Q will switch to the opposite of its previous state.

- 😀 Unlike RS flip-flops, where both Set and Reset inputs being active simultaneously leads to an invalid state, JK flip-flops can handle both J and K being 1 by toggling the output.

- 😀 The JK flip-flop circuit can be simulated using a software tool to observe the output changes when different input combinations are applied, helping visualize its behavior.

- 😀 The JK flip-flop's truth table shows how different combinations of inputs affect the Q and Q' outputs. For instance, J=K=0 keeps the previous state.

- 😀 In the simulation, the clock signal triggers the JK flip-flop to update its state based on the J and K inputs, and this is reflected in the LED indicators connected to the output.

- 😀 The RS flip-flop is similar to the JK flip-flop but with a limitation: when both Set and Reset are active, it creates an invalid state, while the JK flip-flop handles it by toggling outputs.

- 😀 The preset and clear inputs (which are often part of the JK flip-flop) force the outputs to specific states. The preset sets Q to 1, and clear sets Q to 0.

- 😀 The demonstration also highlights the importance of proper circuit connections, including the use of power, ground, and clock signals, to ensure the JK flip-flop operates correctly during simulation.

Q & A

What is the primary difference between JK flip-flop and RS flip-flop?

-The primary difference is that JK flip-flop uses J and K inputs, whereas RS flip-flop uses set and reset inputs. The JK flip-flop behaves differently when both J and K inputs are set to 1, toggling the output to the opposite of its previous state, unlike the RS flip-flop.

How does the clock input affect the JK flip-flop?

-The clock input in a JK flip-flop triggers the state change of the outputs (Q and Q'). The clock pulse ensures that the flip-flop updates its state based on the values of the J and K inputs at the time of the pulse.

What happens when both J and K are 1 in a JK flip-flop?

-When both J and K are set to 1, the JK flip-flop's output toggles, meaning it changes to the opposite of its previous state. This is in contrast to other states where the output follows a more predictable pattern based on J and K values.

What role do the preset and clear inputs play in a flip-flop circuit?

-Preset and clear inputs are used to directly set or reset the output. The preset input forces the output Q to 1, while the clear input forces it to 0, regardless of the state of the J and K inputs.

What happens when both preset and clear inputs are active at the same time?

-When both preset and clear inputs are active, the output behavior can become unpredictable or contradictory. The standard design of flip-flops usually prevents this condition, but if it occurs, it typically results in an undefined state.

How does the truth table for JK flip-flops define the behavior of the outputs?

-The truth table for JK flip-flops specifies the state changes based on the values of J, K, and the clock signal. For example, when J is 1 and K is 0, the output Q becomes 1. Similarly, when both J and K are 0, the output maintains its previous state.

Why did the instructor encounter issues during the simulation of the JK flip-flop?

-The issues encountered were due to a simulation program error, which caused the expected output changes to not appear correctly. Despite this, the instructor verified that the circuit itself was functioning correctly by checking the clock pulse and input signals.

What is the significance of the feedback loop in the JK flip-flop circuit design?

-The feedback loop in the JK flip-flop ensures that the output can toggle based on the inputs J and K. This feedback mechanism allows the flip-flop to store its previous state and toggle between states when the clock pulse occurs.

In the JK flip-flop, what happens when both J and K are 0?

-When both J and K are 0, the JK flip-flop retains its previous state. The output Q will not change, effectively 'holding' the output at its last value.

How is a JK flip-flop different from a D flip-flop or T flip-flop?

-A JK flip-flop is more versatile than a D or T flip-flop because it allows independent control over the set and reset behaviors through its J and K inputs. In contrast, a D flip-flop has a single data input, and a T flip-flop toggles based on the input value. JK flip-flops can function in both set and reset modes, making them more flexible.

Outlines

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードMindmap

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードKeywords

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードHighlights

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードTranscripts

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレード5.0 / 5 (0 votes)