Page Tables and MMU: How Virtual Memory Actually Works Behind the Scenes (Animation)

Takeaways

- 🖥️ Chaque processus possède une table de pages qui mappe les pages mémoire virtuelles aux cadres mémoire physiques.

- 📊 Une entrée de table de pages (PTE) contient le numéro du cadre physique, des bits de permission et des bits de statut.

- 🔒 Les bits de permission incluent lecture seule, utilisateur/superviseur et exécution interdite pour protéger la mémoire.

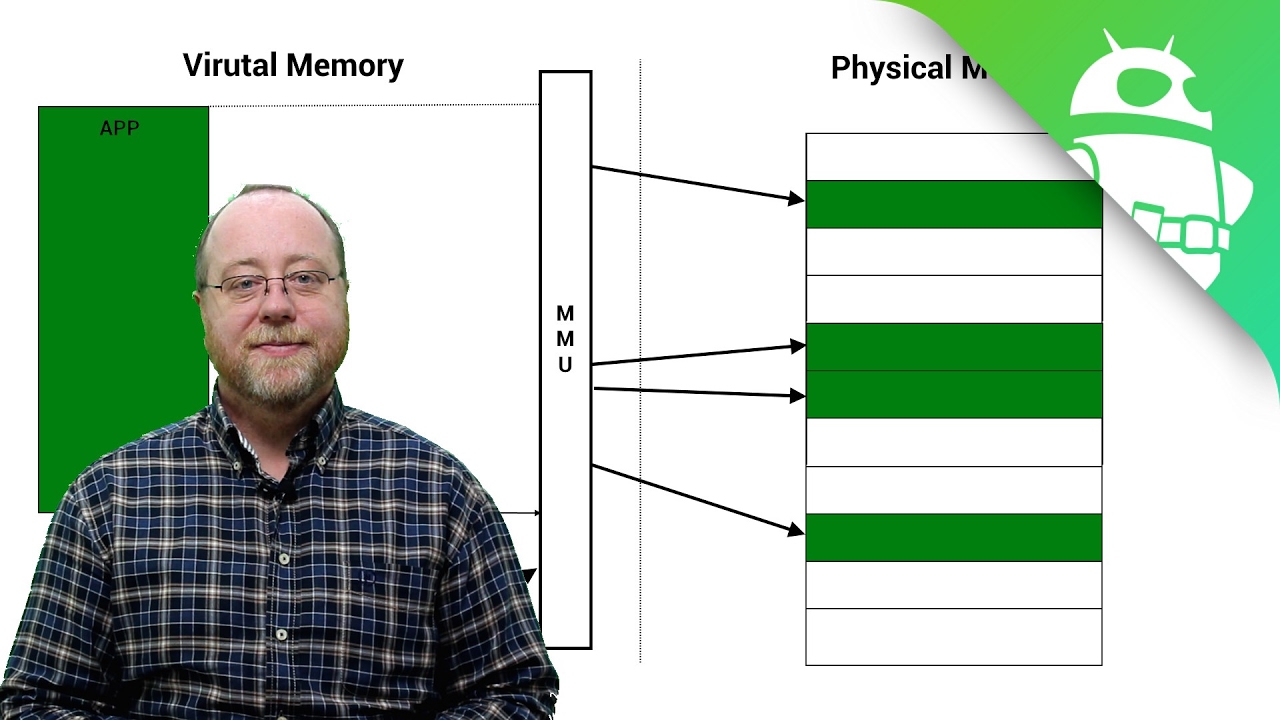

- ⚡ L'unité de gestion de mémoire (MMU) traduit les adresses virtuelles en adresses physiques et applique les permissions.

- 💾 La Translation Lookaside Buffer (TLB) est un cache qui accélère la traduction des adresses virtuelles en adresses physiques.

- ⏱️ Si une adresse virtuelle n'est pas trouvée dans la TLB (TLB miss), le MMU consulte la table de pages complète en RAM.

- ❗ Un défaut de page (page fault) se produit si la page demandée n'est pas en mémoire ou si l'entrée de la table est invalide.

- 🧠 La TLB utilise des politiques de remplacement comme LRU, round-robin ou aléatoire pour gérer les entrées lorsqu'elle est pleine.

- 📐 Les tables de pages peuvent devenir très grandes (ex. 16 Go de mémoire virtuelle avec pages de 4 Ko → ~4,2 millions d'entrées).

- 🔄 Lors d'un changement de contexte, le registre de base de la table de pages est mis à jour pour pointer vers la table active du processus.

- 🛡️ Les bits de statut (présent, modifié, accédé, global) aident le MMU à gérer efficacement la mémoire et les partages entre processus.

- 🏎️ Les systèmes modernes utilisent une hiérarchie de TLB pour améliorer les taux de succès, similaire aux caches d'instructions et de données.

Q & A

Qu'est-ce qu'une table de pages et pourquoi est-elle utilisée dans la gestion de la mémoire virtuelle ?

-Une table de pages est une structure de données utilisée par le système d'exploitation pour gérer la traduction des adresses virtuelles en adresses physiques. Chaque entrée de la table contient l'adresse physique d'un cadre de mémoire ainsi que des informations supplémentaires, telles que des bits de protection et d'état.

Pourquoi la taille de la table de pages peut-elle devenir un problème dans un système moderne ?

-La taille des tables de pages peut devenir problématique car elles peuvent contenir des millions d'entrées, chacune nécessitant plusieurs octets pour stocker l'information. Par exemple, dans un espace mémoire virtuel de 16 Go avec une taille de page de 4 Ko, il peut y avoir 4,2 millions d'entrées. Cela représente une consommation significative de mémoire, ce qui peut être inefficace et coûteux en termes de ressources.

Quel est le rôle du registre de base de la table de pages (Page Table Base Register) ?

-Le registre de base de la table de pages (Page Table Base Register) est un registre protégé du processeur qui contient l'adresse de la table de pages active d'un processus. Lors d'un changement de contexte, ce registre est mis à jour pour référencer la table de pages du processus en cours d'exécution.

Quels types de bits de protection se trouvent dans une entrée de table de pages ?

-Les bits de protection incluent des bits tels que le bit en lecture seule (qui empêche la modification de la page), le bit utilisateur-superviseur (qui détermine les privilèges d'accès), et le bit d'exécution interdite (qui empêche l'exécution du code de la page, une mesure de sécurité contre certaines attaques).

Pourquoi est-il nécessaire d'utiliser une unité de gestion de la mémoire (MMU) dans un système moderne ?

-L'unité de gestion de la mémoire (MMU) est essentielle pour traduire les adresses virtuelles générées par le processeur en adresses physiques. Elle assure également la protection de la mémoire en empêchant les processus d'accéder à des zones mémoire qui leur sont interdites, et en appliquant des restrictions d'accès pour éviter les attaques malveillantes.

Qu'est-ce qu'un TLB (Translation Lookaside Buffer) et comment accélère-t-il la traduction des adresses ?

-Le TLB est un cache de petites tailles dans la MMU qui stocke des entrées récentes de la table de pages pour éviter des accès mémoire fréquents. Il accélère la traduction des adresses en réduisant le besoin de consulter la table de pages complète à chaque requête.

Quelle est la différence entre un TLB d'instructions et un TLB de données ?

-Le TLB d'instructions est utilisé pour la traduction des adresses des instructions CPU, tandis que le TLB de données traduit les adresses des données. En ayant ces deux types, le système peut optimiser l'accès à la mémoire en fonction du type d'opération effectuée (exécution de code ou manipulation de données).

Qu'est-ce qu'une exception de type 'Page Fault' et comment est-elle gérée ?

-Une exception de type 'Page Fault' se produit lorsque le MMU ne trouve pas l'entrée correspondante dans le TLB ou lorsque l'entrée est marquée comme invalide. Dans ce cas, le système d'exploitation prend le contrôle, vérifie la validité de l'accès et charge la page nécessaire depuis le disque si nécessaire.

Pourquoi la pleine capacité de la mémoire physique est-elle souvent insuffisante pour stocker toutes les tables de pages dans un système multitâche ?

-Dans un système multitâche, chaque processus dispose de sa propre table de pages, et avec des tables de pages volumineuses, cela peut nécessiter des centaines de mégaoctets de mémoire. Cela peut devenir un problème dans les systèmes avec de nombreux processus actifs, d'où la nécessité de techniques d'optimisation.

Que se passe-t-il lorsque le TLB est plein et ne peut pas ajouter de nouvelles entrées ?

-Lorsque le TLB est plein, l'unité de gestion de la mémoire (MMU) doit évincer une entrée existante pour faire place à la nouvelle. Cela se fait généralement en suivant une politique de remplacement, comme la politique du moins récemment utilisé (LRU) ou une politique plus simple comme le remplacement aléatoire.

Outlines

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantMindmap

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantKeywords

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantHighlights

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantTranscripts

Cette section est réservée aux utilisateurs payants. Améliorez votre compte pour accéder à cette section.

Améliorer maintenantVoir Plus de Vidéos Connexes

What is virtual memory? – Gary explains

But, what is Virtual Memory?

Paging in Operating Systems with Example & Working - Memory Management

L-5.9: What is Paging | Memory management | Operating System

Sistemas Computacionais - Técnica de memória virtual: paginação e segmentação

L-5.14: Inverted paging | Memory Management | Operating System

5.0 / 5 (0 votes)