Tutorial-6: QPSK Modulator Design in SystemVue

Summary

TLDRIn this tutorial, the process of designing a QPSK modulator is explained step-by-step. Starting with a fresh schematic, the instructor demonstrates how to place blocks like bits, mappers, filters, and modulators. Key components such as the root raised cosine filter and modulator are used to shape the signal and prepare it for simulation. The tutorial also covers filter synthesis and visualization of the frequency and step responses. Finally, the simulation results are analyzed and plotted, with a focus on modulated output and how to adjust parameters like frequency to optimize the system.

Takeaways

- 😀 A QPSK (Quadrature Phase Shift Keying) modulator is designed using a system design tool that allows for visualizing and simulating modulation processes.

- 😀 The design process starts with creating a new workspace and choosing a blank template for the schematic layout.

- 😀 The key components used in the design include a Bits block, Mapper, Complex Signal, Rectangular to I/Q Converter (C x2), Root Raised Cosine Filter, and Modulator.

- 😀 The Root Raised Cosine Filter is synthesized using a specific filter design with a symbol rate of 5 MHz and 35% excess bandwidth.

- 😀 The complex signal is converted into I/Q data using the C x2 block, which is then filtered to shape the pulses appropriately.

- 😀 The Modulator block combines the I/Q data into a modulated signal for visualization in the spectrum analyzer.

- 😀 Filters are synthesized using the 'Generic Filter Design' block, which supports various filter topologies, and frequency response is analyzed through this process.

- 😀 The simulation is set up with a 10 MHz sample rate and an 8k FFT point to observe the modulated output.

- 😀 The modulated signal's frequency is initially not centered correctly, requiring manual adjustment to 70 MHz for proper visualization.

- 😀 The next tutorial will cover vector demodulation and checking the quality of the modulated signal, extending the understanding of QPSK modulation.

Q & A

What is the purpose of this tutorial?

-The purpose of this tutorial is to guide users through the process of designing a QPSK (Quadrature Phase Shift Keying) modulator using a digital signal processing (DSP) system.

What are the key components used in the QPSK modulator design?

-The key components used in the design include the Bits block, Mapper, Complex-to-Rectangular converter (C x2), Root Raised Cosine Filter, Modulator, and Spectrum Analyzer.

How do you start setting up the QPSK modulator?

-To start, create a new workspace with a blank template. From there, place and wire up the necessary blocks, including the Bits block, Mapper, C x2 converter, and Root Raised Cosine Filter.

What does the Mapper block do in this design?

-The Mapper block maps the input bits to a complex signal, which is essential for modulating the data in a QPSK system.

Why is a Root Raised Cosine Filter used in the QPSK modulator design?

-The Root Raised Cosine Filter is used to shape the signal to avoid inter-symbol interference, ensuring that the modulated signal has the desired bandwidth and time-domain characteristics.

What role does the Modulator block play in the design?

-The Modulator block converts the filtered I/Q data into a complex signal of the form I + jQ, which is the final modulated output for QPSK.

How do you visualize the output of the QPSK modulator?

-The output can be visualized using a Spectrum Analyzer, which provides insights into the frequency characteristics of the modulated signal.

What filter is synthesized in this tutorial, and how is it configured?

-A Root Raised Cosine Filter is synthesized in this tutorial. It is configured with a 10 MHz sample rate, a 5 MHz symbol rate, and a 35% excess bandwidth.

What is the significance of the frequency response graph shown during filter synthesis?

-The frequency response graph illustrates the performance of the synthesized filter, showing how well it shapes the signal and whether it meets the required specifications.

Why is the modulation frequency set to 70 MHz in the simulation?

-The modulation frequency is set to 70 MHz to ensure the output signal is centered at the correct frequency, aligning with the system's design specifications.

Outlines

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenMindmap

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenKeywords

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenHighlights

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenTranscripts

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenWeitere ähnliche Videos ansehen

Tutorial-9: Real Time Tuning of Parameters in SystemVue

Tutorial-7: Vector Modulation Analysis

(Req) Simulasi Pemasangan Instalasi Listrik Rumah

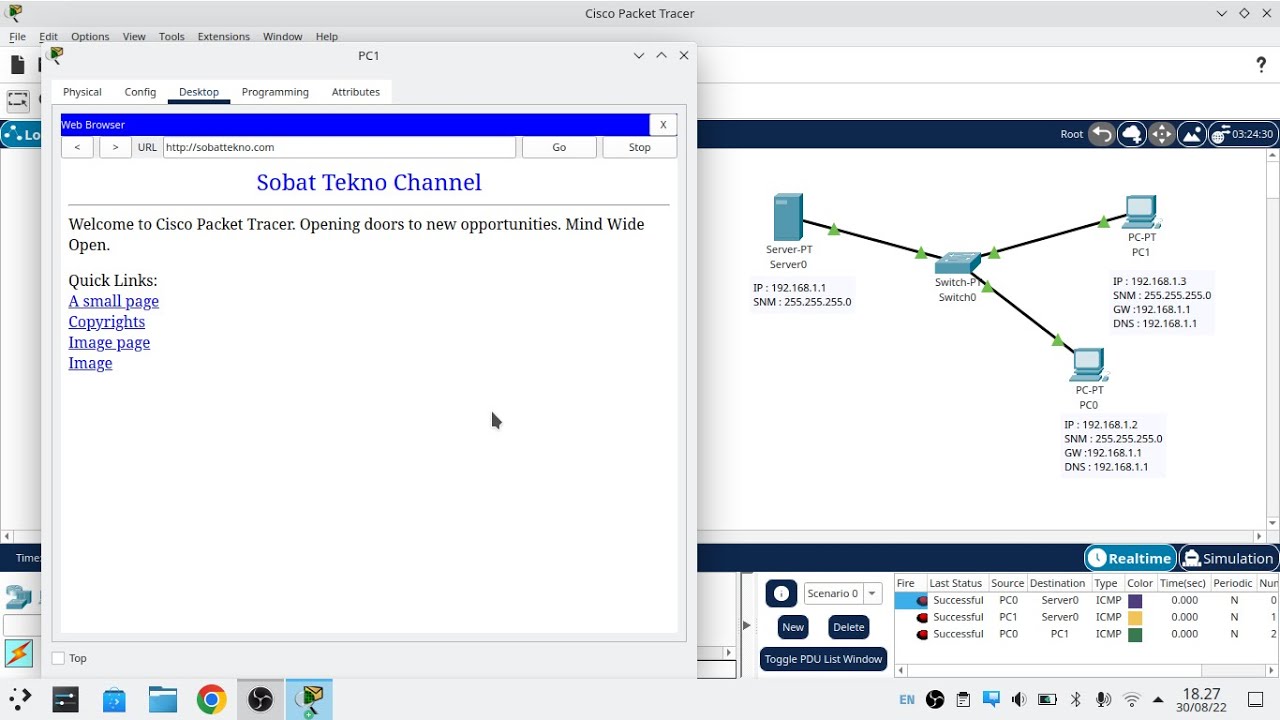

Cara Konfigurasi DNS Server Di Cisco Packet Tracer

Creating a Hello World Application | How-to | Flowable

Tutorial Efiling 2022: Cara Lapor Pajak SPT Tahunan Secara Online Penghasilan Dibawah Rp 60 Juta

5.0 / 5 (0 votes)