Design, Implement, and Visualize: XADC IP for FPGA Temperature Monitoring in Vivado

Summary

TLDRIn this video, the process of using the XADC IP in Xilinx Vivado to measure the die temperature of an FPGA is demonstrated. The tutorial uses a Basis 3 FPGA board and walks through the configuration of the XADC wizard block, enabling temperature measurement and monitoring. The video also covers generating the HDL wrapper, implementing the design, and visualizing the data through a custom dashboard. Viewers are shown how to set update frequencies and configure other analog signals, making the XADC a valuable tool for real-time thermal performance monitoring. The video concludes with tips on further FPGA design projects.

Takeaways

- 😀 XADC IP in Xilinx Vivado allows for monitoring and measuring analog signals directly on the FPGA board.

- 😀 The Basis 3 FPGA board from Digilent is used in the demonstration, but any FPGA board with Xilinx support can be used.

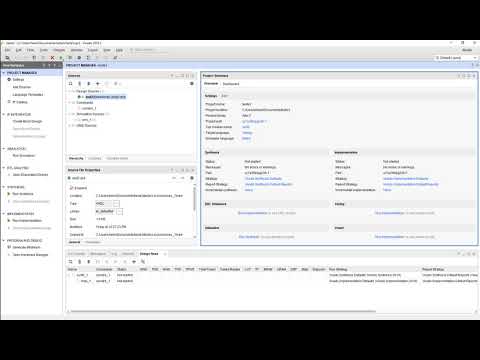

- 😀 The XADC wizard block is configured in Vivado to measure the die temperature of the FPGA.

- 😀 The configuration process involves selecting a channel sequencer and enabling VCCI temperature measurement.

- 😀 HDL code is generated using the source code to wrap the block design into VHDL for further use in the FPGA.

- 😀 XADC IP can monitor the thermal performance of the FPGA board in real time, providing valuable temperature data.

- 😀 Alarms can be configured with XADC to trigger when temperature thresholds are exceeded.

- 😀 After implementing the design in Vivado, a bitstream is generated to configure the FPGA board.

- 😀 A dashboard is created in Vivado’s system monitor to display the FPGA’s die temperature in real-time.

- 😀 Users can adjust the scan rate or update frequency of the temperature reading, with options for 5, 10, 30 seconds, or even 1 minute.

Q & A

What is the purpose of using the XADC IP in Vivado?

-The XADC IP is used to measure and monitor analog signals directly on the FPGA board, such as the die temperature of the FPGA, which helps in assessing its thermal performance.

What FPGA board is used in this tutorial?

-The tutorial uses the Basis 3 FPGA board manufactured by Digilent, although other FPGA boards could also be used.

What does XADC stand for and what is its significance?

-XADC stands for Xilinx Analog to Digital Converter. It is a powerful feature in Xilinx FPGA devices that allows real-time monitoring of analog signals, such as voltage or temperature.

How does the XADC IP measure the die temperature of the FPGA?

-The XADC IP is configured to measure the VCCI NT (voltage) and uses a channel sequencer to monitor the die temperature. The data can be displayed on a dashboard in Vivado.

What is the significance of configuring the XADC wizard block in Vivado?

-Configuring the XADC wizard block in Vivado allows you to set up the measurement parameters (such as temperature or voltage) and convert the block design into VHDL code for implementation on the FPGA.

What is a VHDL wrapper, and why is it needed in this process?

-A VHDL wrapper is used to convert the block design created in Vivado into VHDL code, which can then be implemented and synthesized on the FPGA board.

What step comes after generating the VHDL wrapper for the XADC design?

-After generating the VHDL wrapper, the next step is to run the implementation of the design, followed by generating the bitstream file, which is used to configure the FPGA.

How do you monitor the die temperature of the FPGA in Vivado?

-You can monitor the die temperature by creating a new dashboard in Vivado. This dashboard will display the real-time temperature data measured by the XADC IP.

What was the die temperature displayed on the dashboard in the tutorial?

-The die temperature displayed on the dashboard was around 42°C, while the room temperature was approximately 35°C.

Can you adjust the frequency at which the XADC data is updated?

-Yes, you can configure the update frequency of the XADC data. It can be set to update every 5, 10, 30 seconds, or 1 minute, depending on your needs.

Outlines

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنMindmap

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنKeywords

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنHighlights

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنTranscripts

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنتصفح المزيد من مقاطع الفيديو ذات الصلة

Hello world video using Xilinx Zynq, Vivado 2020, and Vitis

Vivado01 1 Familiarizacao com o Vivado e Simulacao de uma AND2

VHDL code for 4 bit ALU and Realization on FPGA development Board

Calorimetria: calorímetro simples #MArteFisica

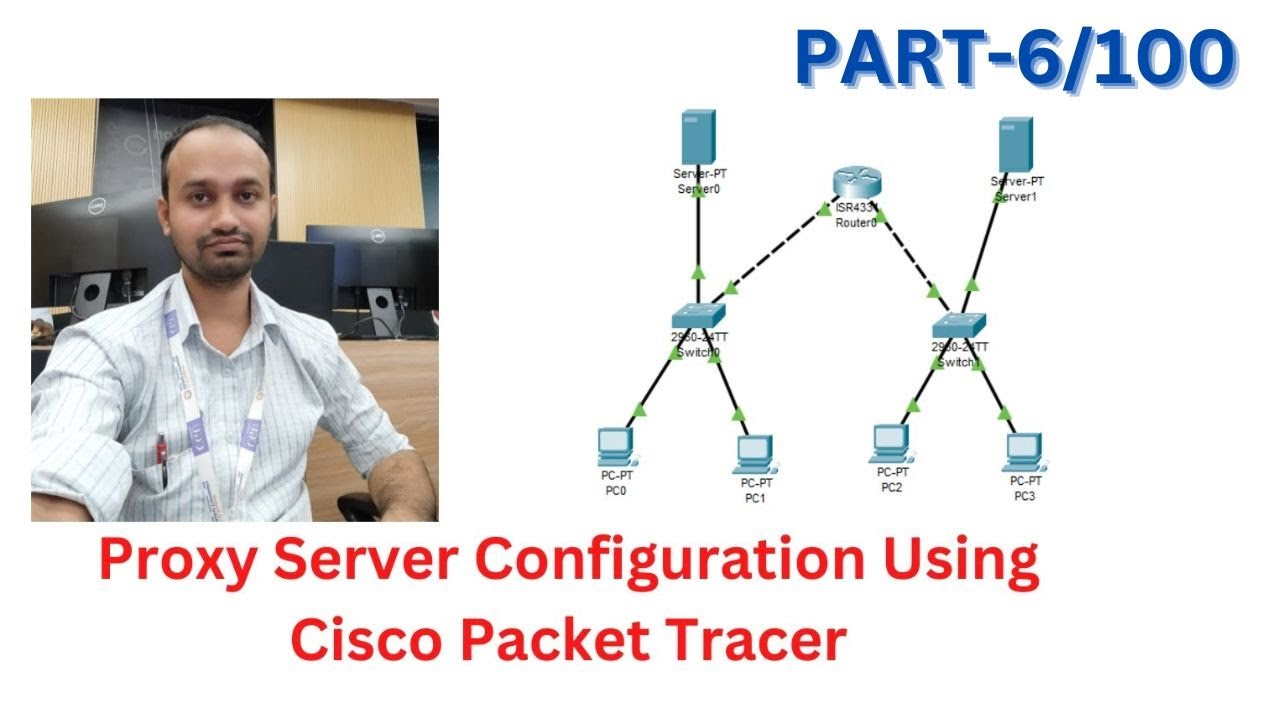

Proxy Server Configuration Using Cisco Packet Tracer in Hindi

#QUÍMICA - MEDINDO PH COM PHMETRO

5.0 / 5 (0 votes)