Image Processing on Zynq (FPGAs) : Part 2 Design of Line buffer

Summary

TLDRThis tutorial covers the development of an image processing IP using neighborhood operations, with a focus on creating a custom line buffer for convolution tasks. The instructor explains the design process for a grayscale image, starting with the line buffer that stores image data for reuse during convolution operations. They emphasize building custom IP over using prebuilt libraries for flexibility and detail the steps for managing read/write operations efficiently. The tutorial introduces handling memory, pixel reading, and writing, simulating the design, and enhancing performance by reducing read latency with prefetching techniques.

Takeaways

- 🖥️ The video covers coding for developing an image processing IP using neighborhood operations.

- 🗂️ The first step is to design a line buffer, which will store one line of a grayscale image, with each pixel being 1 byte.

- 💾 The line buffer is modeled as RAM, not a FIFO, because data needs to be reused multiple times during convolution operations.

- 🎛️ The image size is assumed to be 512x512 pixels, and one pixel is written to the buffer at a time.

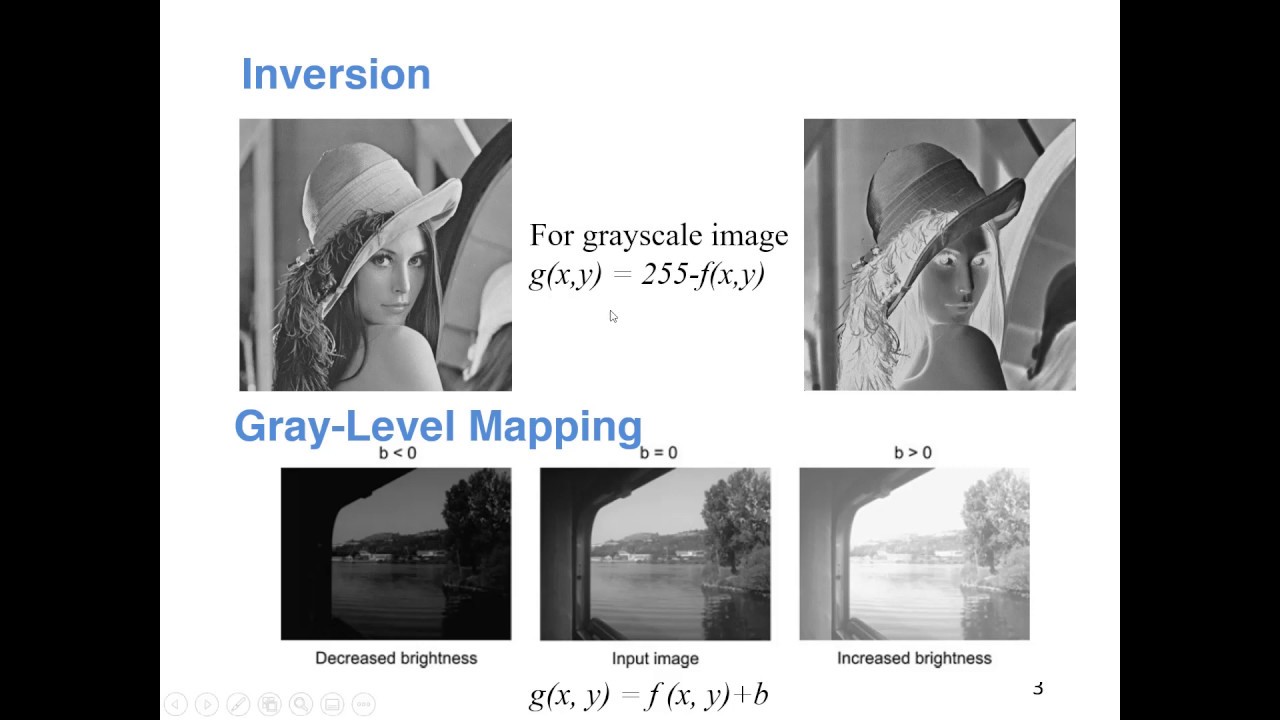

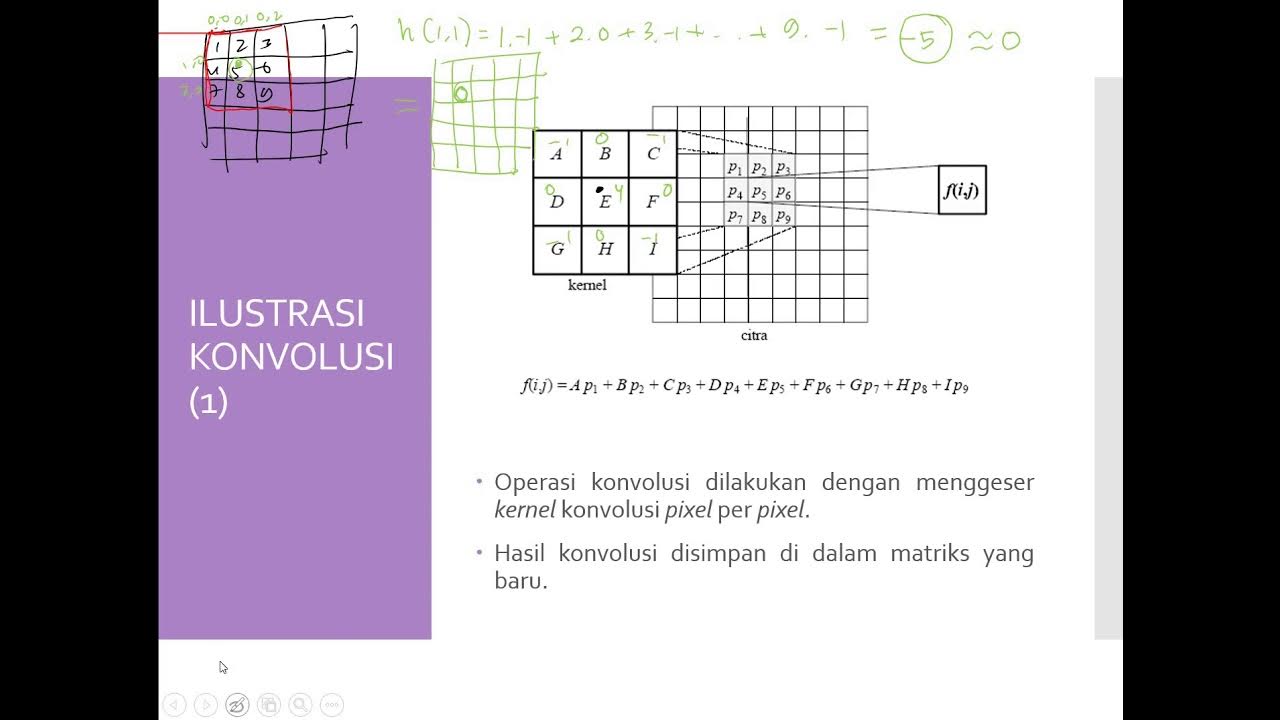

- ⚙️ A 3x3 kernel is used for convolution, requiring three pixels to be read at once from the line buffer, forming a 24-bit data output.

- 📐 Since standard IP cores may not offer the flexibility needed (like reading 24 bits), the speaker suggests writing a custom IP for better control.

- 🔄 The write and read logic for the line buffer are implemented using registers, with separate pointers for write and read operations.

- 📊 The read pointer increments by 1 after each read to account for overlapping data in convolution operations.

- ⏲️ The combinational logic allows prefetching of data, reducing latency by making data available immediately, rather than waiting for the next clock cycle.

- 🏗️ The video emphasizes building custom IP for specific flexibility, like handling asymmetric RAM and avoiding read latency issues.

Q & A

What is the main focus of the tutorial?

-The tutorial focuses on video coding for developing an image processing IP (Intellectual Property) through neighborhood operations, starting with the design of a line buffer.

What type of image is assumed to be processed in the tutorial?

-The tutorial assumes that a grayscale image is being processed, where each pixel is one byte.

Why is a line buffer used in the design?

-A line buffer is used to store one line of an image, facilitating the initial filling of data from the original image and subsequent read-out for processing.

Why can't a FIFO (First-In-First-Out) model be used for the line buffer in this context?

-A FIFO model cannot be used because it allows data to be read only once, whereas convolution operations may require the reuse of the same data multiple times.

What is the significance of using a dual-port DRAM for the line buffer?

-Using a dual-port DRAM allows for simultaneous read and write operations, which is essential for the line buffer to function effectively in image processing.

What are the two main assumptions made for the line buffer design?

-The two main assumptions are: 1) Writing one pixel at a time to the line buffer, and 2) Assuming the size of the image is 512x512, requiring the buffer to store 512 pixels.

Why is the 'ready' signal not included in the line buffer's interface?

-The 'ready' signal is not included because memory is always ready to accept data; there is no case where the memory cannot accept data due to being busy.

How does the output interface of the line buffer differ when reading multiple pixels at once?

-When reading multiple pixels at once, the output interface must accommodate the combined width of the pixels being read. For example, if reading three 8-bit pixels, the output width would be 24 bits.

What is the purpose of the 'read_data' signal in the line buffer?

-The 'read_data' signal indicates when data should be read from the line buffer, similar to the 'valid' signal in an AXI stream interface.

Why is it beneficial to use a combinational logic for the read pointer instead of a sequential one?

-Using a combinational logic for the read pointer allows for zero latency between the 'read_data' signal and the output of the actual data, making the system more efficient.

How does the tutorial demonstrate the functionality of the line buffer through simulation?

-The tutorial simulates the line buffer by storing and reading data, showing how the write and read pointers increment and how data is prefetched for immediate output.

Outlines

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنMindmap

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنKeywords

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنHighlights

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنTranscripts

هذا القسم متوفر فقط للمشتركين. يرجى الترقية للوصول إلى هذه الميزة.

قم بالترقية الآنتصفح المزيد من مقاطع الفيديو ذات الصلة

5.0 / 5 (0 votes)