Introduction

Summary

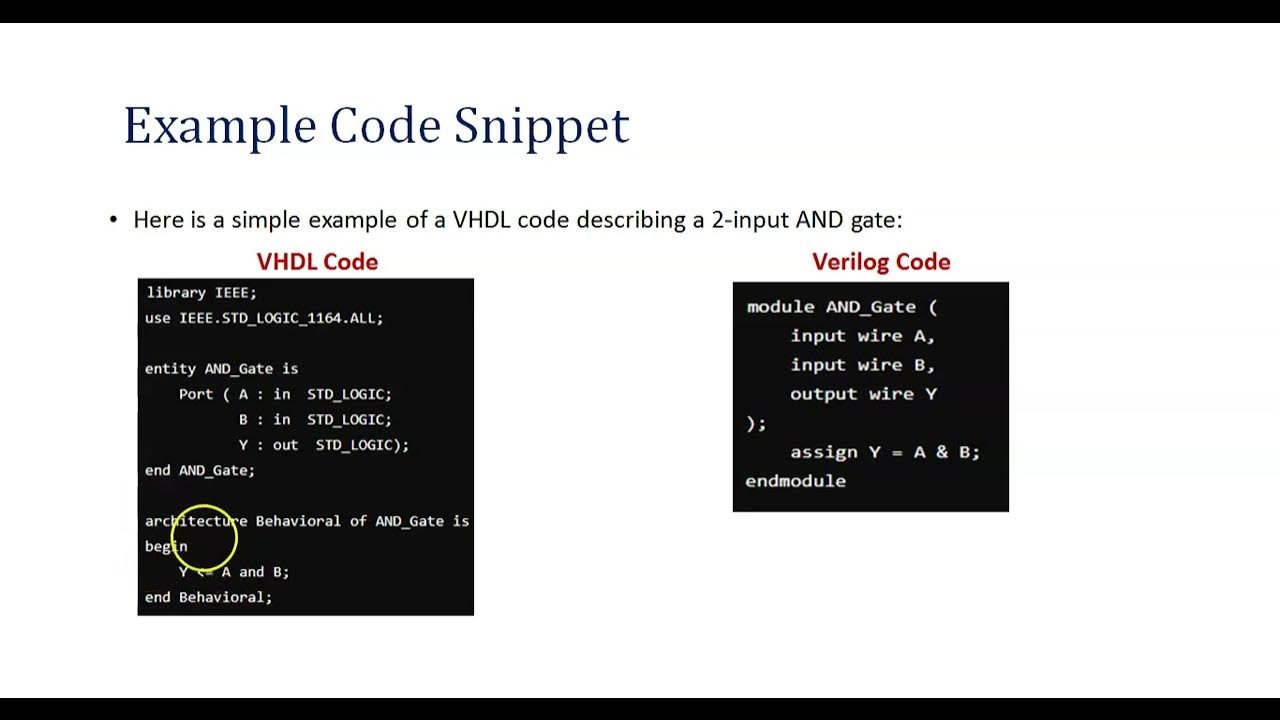

TLDRThis course introduces Hardware Modeling using Verilog, a language for specifying hardware behavior, functionality, or structure. Over eight weeks, students will explore Verilog's features, learn behavioral and structural design styles, and write test benches for verification. The course covers modeling of combinational and sequential circuits, good practices, and case studies, including processor design. It also provides an overview of the VLSI design process, emphasizing the importance of CAD tools and the impact of Moore's Law on semiconductor advancements.

Takeaways

- 📘 The course is an 8-week introduction to Verilog, a hardware description language used for specifying the behavior or structure of hardware circuits.

- 🛠️ Verilog allows designers to model functionality in two distinct styles: behavioral and structural, and the course will cover the differences between them.

- 🔍 Students will learn to write test benches for verifying the correctness of hardware designs through simulation.

- 🔌 The course will cover modeling of both combinational and sequential circuits, essential for understanding digital logic design.

- 🛡️ Good practices and avoidable practices in Verilog design will be discussed to enhance the quality of the designs.

- 💡 Case studies, including the design of a complete processor, will be used to illustrate the application of Verilog in complex hardware design.

- 📈 VLSI design complexity has increased dramatically over the years, moving from hundreds of components to billions of transistors in a single chip.

- 🛑 The manual design of circuits is no longer feasible due to their complexity, necessitating the use of computer-aided design (CAD) tools.

- ⚙️ VLSI design involves balancing conflicting requirements such as reducing area, increasing speed, and lowering energy consumption.

- 📉 Moore's Law, which predicts the doubling of transistors on a chip every 18 months, has held true and continues to drive advancements in semiconductor design.

- 🌐 CMOS technology, including innovations like FinFET, enables the miniaturization of transistors and the continued relevance of Moore's Law.

- 🔩 The VLSI design flow is a standardized procedure that includes steps from specification to hardware manufacturing, heavily reliant on CAD tools and HDLs like Verilog.

Q & A

What is the main focus of the course on Hardware Modeling using Verilog?

-The course focuses on teaching the Verilog hardware description language, its features, syntaxes, and how to utilize them for hardware design, including behavioral and structural design styles.

What are the two distinct ways of modeling the functionality of a circuit mentioned in the course?

-The two distinct ways of modeling the functionality of a circuit are behavioral and structural design styles.

What is a test bench in the context of hardware design?

-A test bench is a piece of code used to verify whether a hardware design is working correctly. It is used to evaluate the results of simulations.

What does the VLSI design process involve?

-The VLSI design process involves a series of steps starting from the specification of the design to the actual hardware circuit fabrication, including synthesis, simulation, layout generation, and testability analysis.

How has the complexity of VLSI circuits evolved over the years?

-The complexity of VLSI circuits has increased dramatically over the years, with an exponential growth in the number of transistors that can be integrated into a single chip, moving from hundreds or thousands to billions.

What is Moore's Law and how does it relate to the semiconductor industry?

-Moore's Law is the observation that the number of transistors on a chip doubles approximately every 18 months, indicating an exponential growth in the semiconductor industry. It has been a driving principle for advancements in chip design and fabrication.

What is the significance of CMOS technology in VLSI design?

-CMOS technology is the most dominant technology used in manufacturing VLSI chips. The shrinking of CMOS transistors has enabled the continued growth in the number of transistors that can be placed on a chip, sustaining Moore's Law.

What is a netlist in the context of hardware design?

-A netlist is a graphical representation where vertices indicate components and edges indicate interconnects, used to specify how different functional blocks are interconnected at various levels of abstraction.

What is the purpose of simulation in the VLSI design flow?

-Simulation is a crucial step in the VLSI design flow for verification purposes. It is used to check and ensure that the Verilog modules meet the design specifications and are functioning as intended.

What are the conflicting requirements that a designer may face during the VLSI design process?

-Designers may face conflicting requirements such as reducing the area, increasing the speed, and minimizing energy consumption. Optimizing one aspect may adversely affect another, making it a challenge to balance these requirements.

What is the alternative to chip fabrication mentioned in the script?

-An alternative to chip fabrication is using a Field Programmable Gate Array (FPGA), which allows for greater flexibility and the ability to program the device directly in the field, although it may offer lower speeds compared to fabricated chips.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

5.0 / 5 (0 votes)