Immediate Assertions in SystemVerilog || All about VLSI ||

Summary

TLDRIn this video, the presenter explains immediate assertions in SystemVerilog, which are used for instantaneous condition checking within procedural blocks such as always, initial blocks, and tasks. Immediate assertions are similar to if-else statements and help debug by identifying incorrect values right away. The video demonstrates how the assert keyword works, using an example where it checks the logical OR of two registers. The video also highlights that immediate assertions cannot be used for checking sequential properties across multiple clock cycles and concludes by inviting viewers to comment and subscribe.

Takeaways

- 😀 Immediate assertions in SystemVerilog are used to check conditions instantaneously as they are encountered in the code.

- 😀 These assertions are similar to `if-else` statements and are commonly used within `always`, `initial` blocks, or tasks in SystemVerilog.

- 😀 Immediate assertions can only be used inside procedural blocks (e.g., `always`, `initial`, tasks) and cannot be used outside of these blocks.

- 😀 The keyword `assert` is used to perform the assertion check on the condition, and it checks if the condition is true or false.

- 😀 If the condition in the assertion is true, the assertion passes; if it's false, the assertion fails.

- 😀 Immediate assertions help in debugging by identifying incorrect values right away.

- 😀 These assertions are checked instantaneously at every point in time during code execution, ensuring immediate validation of conditions.

- 😀 Immediate assertions cannot be used to check sequential properties over multiple clock cycles.

- 😀 A simple example of an immediate assertion: `assert (m || n)` checks if either `m` or `n` is true, passing the assertion if so.

- 😀 Immediate assertions can display error messages using `$display` when a condition fails, helping to identify issues instantly.

- 😀 Immediate assertions are a useful tool for ensuring that certain conditions are met in real-time, improving the debugging process.

Q & A

What are immediate assertions in SystemVerilog?

-Immediate assertions in SystemVerilog are used to check conditions instantaneously when they are encountered in the procedure flow of the code. They function similarly to 'if-else' statements and are used within procedural blocks such as 'always', 'initial', or 'task'.

Where can immediate assertions be used in SystemVerilog?

-Immediate assertions can only be used inside procedural blocks such as 'always', 'initial', or 'task'. They cannot be used outside these blocks.

What is the main purpose of using immediate assertions in code?

-The main purpose of immediate assertions is to check conditions in real time, which helps in debugging by identifying incorrect values instantly, without waiting for multiple clock cycles.

What happens if the condition in an immediate assertion is true?

-If the condition in an immediate assertion is true, the assertion passes, meaning no error is triggered.

What happens if the condition in an immediate assertion is false?

-If the condition in an immediate assertion is false, the assertion fails and typically triggers an error message or behavior specified by the developer, such as using '$display' to print an error.

How does an immediate assertion work in the example provided in the video?

-In the example where the assertion is 'assert (m | n)', the logical 'or' operation of 'm' and 'n' is checked. If either of them is non-zero, the assertion passes. If both are zero, the assertion fails.

Can immediate assertions be used to check conditions across multiple clock cycles?

-No, immediate assertions cannot be used to check sequential properties across multiple clock cycles. They are only for checking conditions instantaneously, at each time step.

What is an example of how immediate assertions can help with debugging?

-Immediate assertions help with debugging by allowing developers to catch errors immediately. For example, if a signal is supposed to be valid but is not, an immediate assertion can trigger an error message right away, which helps pinpoint issues faster.

What is the role of the 'assert' keyword in SystemVerilog?

-The 'assert' keyword in SystemVerilog is used to perform assertion checking, ensuring that specified conditions are true. If the condition fails, the assertion is considered failed, and it may trigger an error or a debugging message.

What does the assertion 'assert(data_valid == 1) else $display("Data is invalid")' do?

-This assertion checks if the signal 'data_valid' is equal to 1. If it is not, it triggers the '$display' function to print 'Data is invalid', indicating a failure in the assertion.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

Introduction to SystemVerilog Assertions | Black Box vs White Box Verification Explained

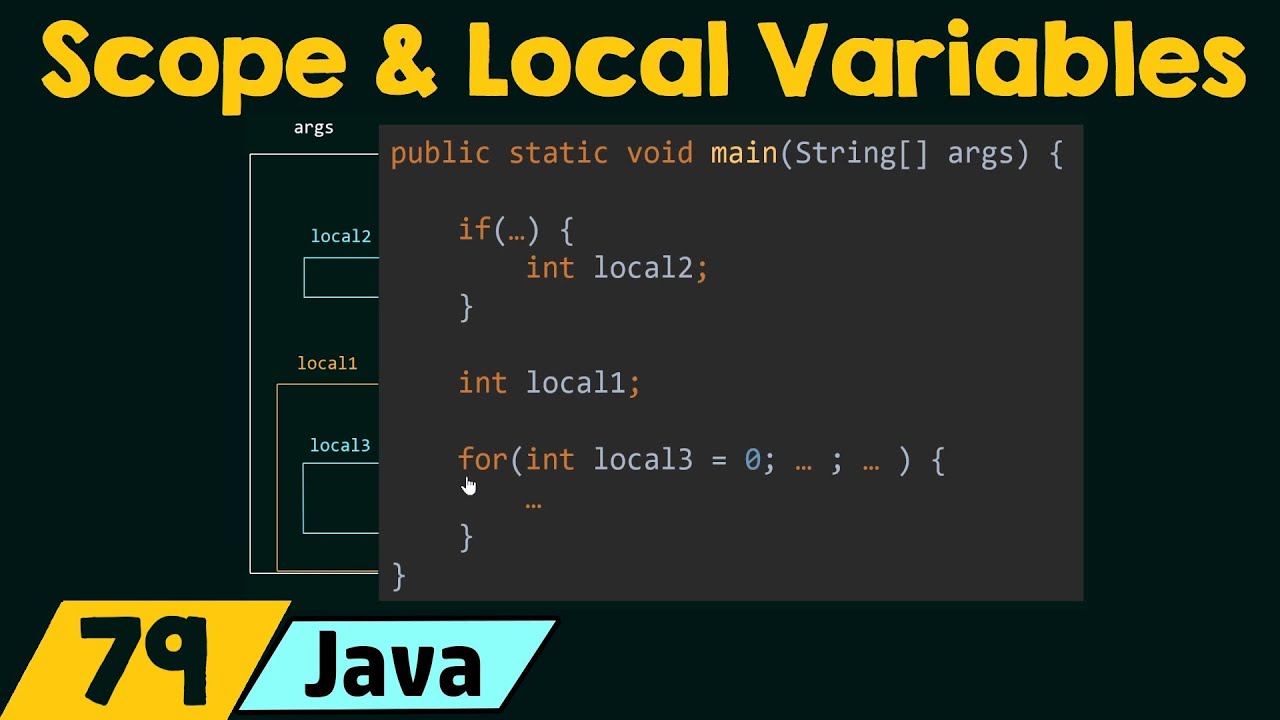

Scope and Local Variables in Java

Verilog Assignment Explain In Telugu || continuous assignments and procedural assessment

Mitigation Blocks Simplified - ICT Concepts

Learn Python EXCEPTION HANDLING in 5 minutes! 🚦

How To Identify and Trade with Rejection Blocks ICT Concept

5.0 / 5 (0 votes)