ASML's High-NA EUV Lithography: A 2024 Update

Summary

TLDRASML's High-NA EUV technology, aimed at advancing Moore's Law, brings both exciting potential and significant challenges. The new system promises to shrink chip features to 7.5-8nm, but with reduced mask field sizes and the need for intricate in-die stitching, it introduces complex issues. These include higher defect rates, thinner resist layers, and the need for new metrology and computational lithography methods. While Intel is trialing the technology, the high cost of ownership and throughput issues remain obstacles. The video discusses the technical hurdles and potential innovations in lithography, including new resist materials and the future role of computational models in improving chip design and production.

Takeaways

- 😀 High-NA EUV is ASML's next-generation lithography technology, designed to continue Moore's Law by significantly reducing the size of semiconductor features.

- 😀 ASML is ramping up production of High-NA EUV machines, with plans to deliver 20 machines annually by 2028, and has already delivered an early model to Intel for testing.

- 😀 One of the challenges of High-NA EUV is the reduced mask field size, requiring the use of in-die stitching to expose larger dies, which introduces alignment and reflection issues.

- 😀 The stitching region where multiple exposures overlap introduces complications, including border reflections that can blur the image, creating challenges in achieving precise patterns.

- 😀 Advances in resist materials, such as Metal Oxide Resists (MORs), show promise for improving the quality and throughput of High-NA EUV, offering more precise printing and higher resistance to etching.

- 😀 The move from traditional Chemical Amplified Resists (CARs) to MORs is a potential shift in the lithography industry, although it may necessitate changes throughout the entire lithography process.

- 😀 Metrology plays a crucial role in ensuring the accuracy of High-NA EUV, as smaller feature sizes require more frequent and precise inspections, often using electron microscopy to detect defects at the sub-nanometer level.

- 😀 Computational lithography, especially tools like Nvidia's CuLitho, is becoming increasingly important in optimizing chip designs for High-NA EUV, helping to detect hotspots and reduce defects.

- 😀 Despite its potential, High-NA EUV faces economic challenges, with the high cost of the machines and the need for higher EUV photon power, which impacts throughput and raises the cost of ownership.

- 😀 TSMC has not yet adopted High-NA EUV machines in bulk, signaling that the cost and efficiency of the technology still need to improve before it becomes widely adopted across the semiconductor industry.

Q & A

What is High-NA EUV and how does it differ from traditional EUV lithography?

-High-NA EUV is a next-generation lithography technology developed by ASML, which increases the Numerical Aperture (NA) from 0.33 to 0.55. This allows for smaller features on semiconductor chips, theoretically shrinking line sizes by 64%. The key difference from traditional EUV is the larger NA, which requires more advanced optics and adjustments in the system's architecture.

Why does High-NA EUV require the use of stitching, and what challenges does it present?

-High-NA EUV reduces the mask field size, meaning that larger dies require multiple exposures. This process, known as in-die stitching, involves overlapping sections of the mask in a way that may cause mechanical stresses and image blurring due to the reflective borders of the photomask. The challenges include precise alignment and minimizing defects in the stitching region.

What role does computational lithography play in High-NA EUV?

-Computational lithography plays a significant role in High-NA EUV by adjusting designs and simulating how masks will behave under the new parameters. This includes techniques like Optical Proximity Correction and Inverse Lithography Technology, which help improve print quality and mitigate the challenges posed by the higher resolution and thinner resist layers.

What is the significance of the resist in High-NA EUV, and why is it a challenge?

-The resist in High-NA EUV is critical for transferring the design onto the wafer. However, the thinner depth of focus requires using thinner resist layers, which leads to challenges in achieving clear images. The resist must also be sensitive to EUV light, and existing organic resists (CARs) struggle with the required precision and defect rates. New alternatives like Metal Oxide Resists (MORs) show promise for better performance.

How does ASML plan to address the throughput issues related to High-NA EUV?

-ASML faces throughput challenges due to the low power of the EUV source. To compensate, they are working on increasing the frequency of tin droplet production and optimizing the power source design. However, there is uncertainty about whether these changes will provide enough power to meet the throughput needs of High-NA EUV.

What is the main competitor to High-NA EUV, and why is it still a viable option?

-The main competitor to High-NA EUV is ASML's own Low-NA EUV machine. While High-NA EUV provides superior resolution, its high cost and throughput issues make multiple passes of Low-NA EUV a more economical option for some applications, at least until the cost of ownership for High-NA EUV comes down.

Why are chip designers considering smaller chiplet designs in the context of High-NA EUV?

-Chip designers are considering smaller chiplet designs to avoid the complexities and potential defects associated with stitching in High-NA EUV. By creating smaller, separate chiplets that can be packaged together, they can avoid the challenges of stitching and still achieve high performance, similar to what is being done with the AMD MI300.

What are the main challenges with metrology in High-NA EUV?

-Metrology in High-NA EUV faces significant challenges due to the need for higher precision in measuring sub-nanometer features. With smaller feature sizes and thinner resist layers, existing tools are less effective. There is a shift towards using electron beam-based metrology tools, such as Transmission Electron Microscopes, to detect defects and ensure high-quality fabrication.

How does ASML plan to overcome the challenges in metrology for High-NA EUV?

-ASML and its partners are focusing on advanced metrology techniques, including the use of electron beam-based tools, to detect smaller defects. There's also an emphasis on computational approaches like 'massive metrology' to inspect many features simultaneously, helping to identify defects at an earlier stage in the manufacturing process.

What are the potential long-term solutions for the high cost and challenges of High-NA EUV?

-In the long term, the solution to the high cost and technical challenges of High-NA EUV may involve improvements in the power source, more efficient computational lithography models, and possibly the use of new resist materials like MORs. Additionally, improvements in metrology and new technologies like Directed Self-Assembly (DSA) may help reduce defects and improve cost efficiency.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

What’s Next For ASML?

Chip 0.5 Nm Segera Diproduksi? ASML Telah Membuat Terobosan Mesin Litografi Next Generation

Why The World Relies On ASML For Machines That Print Chips

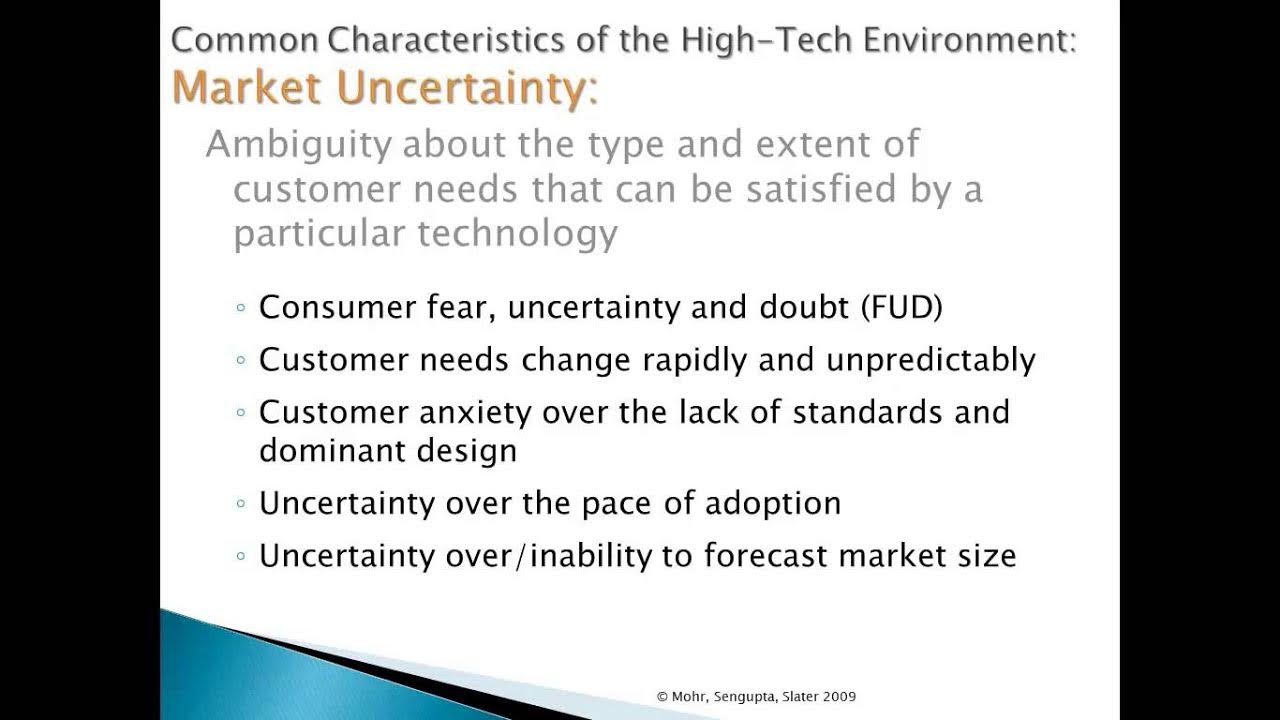

Chapter 1 Intro to High-Tech Marketing

Lịch Sử In 3D - "Chìa Khoá" Của Công Nghệ Tương Lai Và Mặt Trái Đáng Sợ

Samsung Semiconductor Explains Photo Lithography and EUV in 5 Minutes

5.0 / 5 (0 votes)