Understanding Filler Cells in VLSI: A Comprehensive Guide

Summary

TLDRThis video explores the critical role of filler cells in VLSI design, particularly during ASIC implementation. It begins by explaining the layout of standard cells and the necessity of filler cells to optimize area and maintain electrical continuity. The video delves into design automation processes for placing these cells, detailing the methodologies used by industry-standard EDA tools. It also covers the physical design and verification aspects, including DRC compliance to ensure proper implant area and spacing constraints. Viewers are encouraged to engage with related content on decap cells and ESD prevention, making it an informative resource for professionals in the field.

Takeaways

- 😀 Filler cells are essential in VLSI design, ensuring proper spacing and continuity in the chip layout.

- 😀 Standard cells in ASIC design have equal heights, typically referred to as 60 or 90 track cells, affecting layout optimization.

- 😀 The placement of standard cells is designed to ensure continuous wells across rows, aiding in the fabrication process.

- 😀 Filler cells and decap cells fill the empty spaces in standard cell layouts, optimizing area and maintaining functionality.

- 😀 Design automation is crucial for inserting filler cells efficiently in large designs, especially for multi-million gate systems.

- 😀 EDA tools use scripting to automate the placement of filler cells, ensuring compliance with design rules and power rail integrity.

- 😀 Filler cells connect to active implants and power rails, helping maintain the substrate resistance and reducing IR drop issues.

- 😀 Physical design rules dictate the minimum implant and spacing requirements, which filler cells help satisfy.

- 😀 Proper density of filler cells and decaps is necessary to ensure a physically feasible mask for fabrication.

- 😀 DRC (Design Rule Check) is used to verify the placement of filler cells to meet the final design specifications before tape-out.

Q & A

What are filler cells in VLSI design?

-Filler cells are special cells used in VLSI design to fill up empty spaces left after placing standard cells, ensuring continuity in the layout and supporting the physical design requirements.

At what stage of the ASIC design process are filler cells inserted?

-Filler cells are inserted after all standard cells have been placed and the design has been validated for timing and other requirements.

Why is the arrangement of standard cells important in ASIC design?

-The arrangement of standard cells is crucial as it impacts power distribution, fabrication processes, and the overall effectiveness of the mask design, ensuring proper connections and functionality.

How do filler cells contribute to the physical design aspect?

-Filler cells help connect active implants and power rails throughout the design, maintain necessary densities for effective fabrication, and support the integrity of the layout during the manufacturing process.

What role do design automation tools play in the placement of filler cells?

-Design automation tools streamline the process of filler cell placement by using scripting languages to traverse the layout and insert filler cells where needed, ensuring design rules are met efficiently.

What are decap cells, and how do they differ from filler cells?

-Decap cells are used to mitigate IR drop issues during digital implementation, while filler cells primarily serve to fill gaps in the layout and ensure design continuity without providing functional capabilities.

What is the significance of design rule checks (DRC) in relation to filler cells?

-DRC is important for verifying that the design adheres to specific fabrication rules, such as minimum implant areas and spacing constraints, which filler cells help satisfy by filling in gaps as needed.

What factors influence the width and placement of filler cells?

-The width of filler cells is determined by the integer multiples of the routing tracks in the layout, and their placement is influenced by the need to maintain continuity in power and diffusion layers.

Why is achieving 100% utilization of standard cells in a layout not practical?

-Achieving 100% utilization is impractical due to the presence of macros and other design elements that cannot be filled entirely with standard cells, leaving gaps that must be addressed with filler cells.

How do filler cells aid in the overall fabrication process of a silicon chip?

-Filler cells ensure that the layout has the necessary density and continuity for effective ion implantation and other physical processes during fabrication, contributing to a well-formed and functional silicon chip.

Outlines

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowMindmap

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowKeywords

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowHighlights

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowTranscripts

This section is available to paid users only. Please upgrade to access this part.

Upgrade NowBrowse More Related Video

PD Lec 8 - Netlists | PD Inputs part-2 | VLSI | Physical Design

What is VLSI | Introduction & Design flow | VLSI | Lec-01

PD Lec 7 - Physical Design Inputs Overview | Tutorial | VLSI | Physical Design

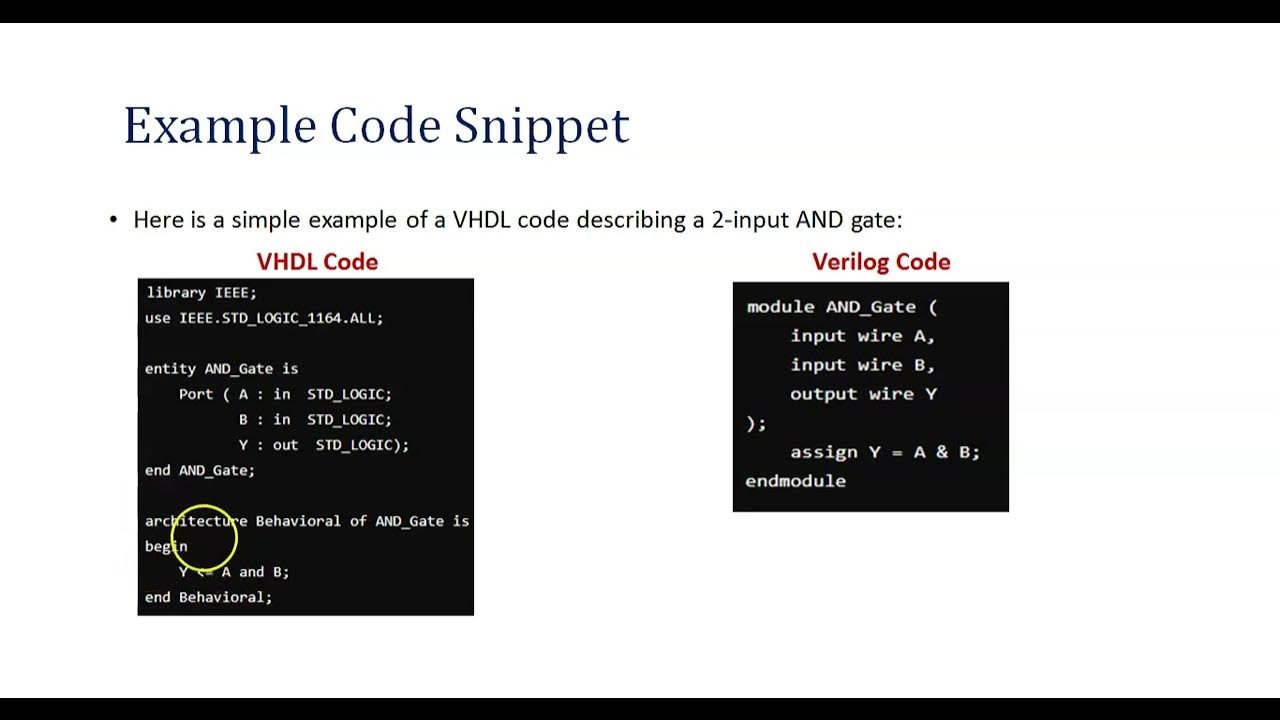

Introduction to HDL (Hardware Description Language)

G11 En bio Ch 1 Act 4 cell renewal Video 2 2020 2021

The best ROADMAP to get into the Semiconductor Industry | Projects level wise | Resources to study

5.0 / 5 (0 votes)