CMOS NAND Gate Explained: Circuit, Working, Implementation, and Truth Table

Summary

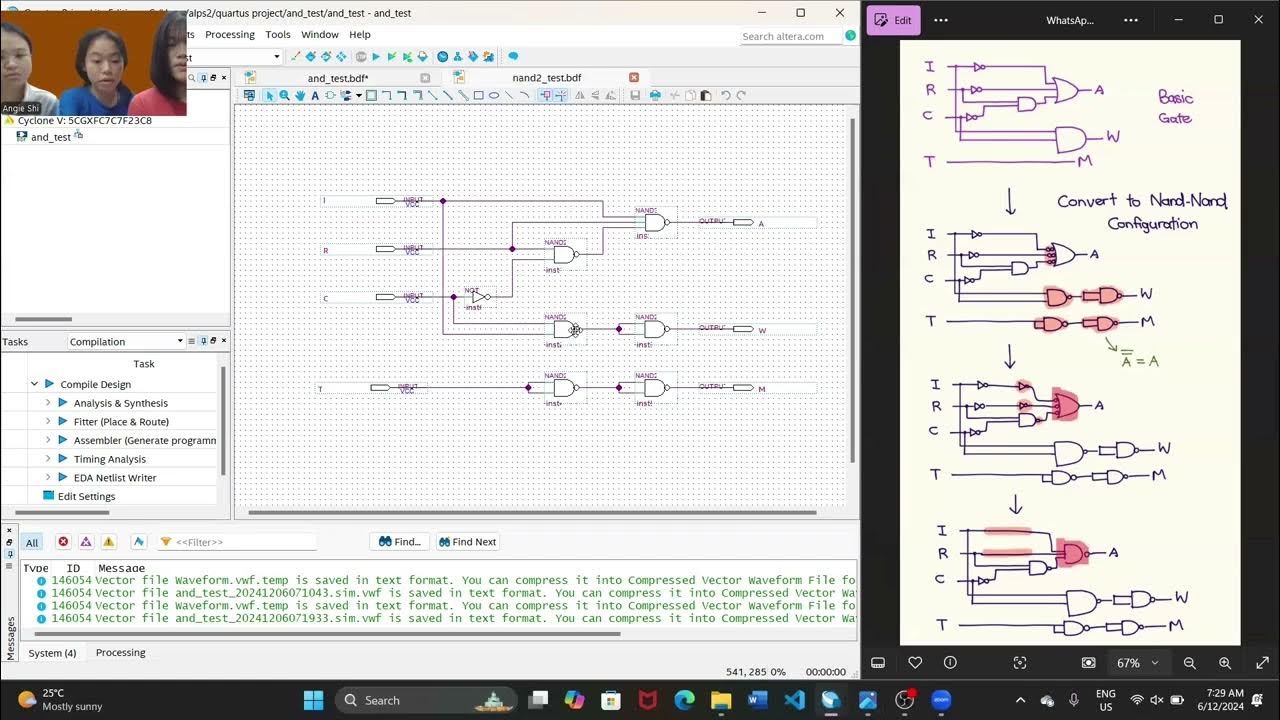

TLDRIn this VLSI lecture, Professor Redes Dolaqia explains the design of a CMOS NAND gate. The lecture covers the basic functionality of a NAND gate, its Boolean equation, and truth table. The professor then details how to implement the NAND gate using CMOS transistors, specifically N-type and P-type MOSFETs (nMOS and pMOS). The explanation includes the pull-up and pull-down networks, the series and parallel connections, and how the circuit operates under different input conditions. The video concludes with a functional analysis of the circuit and a request for viewer feedback.

Takeaways

- 🖥️ The video introduces the design of a CMOS NAND gate, explaining the structure and function of the gate.

- 📝 The NAND gate's Boolean equation is Y = (A ⋅ B)̅, with two inputs, A and B, where the output Y is determined by the logic.

- 🔢 The truth table for the NAND gate shows that if any input is 0, the output will be 1. Only when both inputs are 1 will the output be 0.

- 🔄 The NAND gate is implemented using CMOS transistors, specifically pMOS and nMOS transistors.

- 📶 For the NAND gate, the pull-up network is made with pMOS transistors in parallel, and the pull-down network is made with nMOS transistors in series.

- ⚙️ The basic structure of a CMOS circuit includes a VDD power supply at the top, a pull-up network (pMOS), a pull-down network (nMOS), and an output in between.

- 🔧 The operation of the NAND gate using CMOS transistors depends on the connection of pMOS and nMOS in the circuit, which changes based on the logic values of A and B.

- 📊 When A and B are 0, both pMOS transistors are on and nMOS transistors are off, resulting in a logic 1 output.

- 🧠 The video discusses how pMOS transistors are on when the gate input is 0, and nMOS transistors are on when the gate input is 1.

- 📲 The circuit behavior changes with different combinations of A and B values, explaining how the NAND gate functions through pMOS and nMOS transistor activity.

Q & A

What is the Boolean equation of a NAND gate with two inputs?

-The Boolean equation of a two-input NAND gate is Y = (A · B)'. This means the output Y is the complement of the AND operation between inputs A and B.

What happens to the output of a NAND gate when any of the inputs is 0?

-If any of the inputs to a NAND gate is 0, the output will always be 1.

How many possible input combinations exist for a two-input NAND gate?

-For a two-input NAND gate, there are four possible input combinations: (0,0), (0,1), (1,0), and (1,1).

What is the output of a NAND gate when both inputs are 1?

-When both inputs of a NAND gate are 1, the output will be 0.

How are PMOS and NMOS transistors arranged in a CMOS NAND gate?

-In a CMOS NAND gate, PMOS transistors are arranged in parallel, while NMOS transistors are arranged in series.

What is the role of the pull-up and pull-down networks in a CMOS NAND gate?

-The pull-up network, made of PMOS transistors, is responsible for providing a connection to the positive supply (VDD) when activated, while the pull-down network, made of NMOS transistors, connects the output to ground when activated.

What does it mean for a PMOS transistor to be 'on'?

-A PMOS transistor is considered 'on' when its gate input is at logic 0, causing it to behave like a short circuit.

What is the function of an NMOS transistor when its gate is at logic 1?

-When the gate of an NMOS transistor is at logic 1, the NMOS is 'on' and acts as a short circuit, allowing current to flow.

What is the output of the CMOS NAND gate when both inputs A and B are 0?

-When both inputs A and B are 0, the output will be logic 1, as both PMOS transistors (Q1 and Q2) will be on, and both NMOS transistors (Q3 and Q4) will be off.

How does the CMOS NAND gate function when one input is 0 and the other is 1?

-When one input is 0 and the other is 1, the output will be logic 1 because at least one PMOS transistor will be on and one NMOS transistor will be off, preventing the output from being pulled to ground.

Outlines

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифMindmap

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифKeywords

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифHighlights

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифTranscripts

Этот раздел доступен только подписчикам платных тарифов. Пожалуйста, перейдите на платный тариф для доступа.

Перейти на платный тарифПосмотреть больше похожих видео

5.0 / 5 (0 votes)