DVD - Lecture 6b: Multiple Voltage Domains

Summary

TLDRThis video delves into the complexities of low power design in integrated circuits, focusing on managing multiple voltage domains. It explores the process of defining power domains, placing components strategically, and using power gating techniques to minimize leakage. Key concepts like voltage level shifting and the use of specialized buffers for domain-to-domain communication are discussed. The video also compares CPF and UPF formats for power management, highlighting the challenges and strategies for optimizing power consumption while maintaining functionality across diverse voltage domains.

Takeaways

- 😀 A multi-voltage domain design involves creating separate power domains for different parts of a chip to manage power consumption more effectively.

- 😀 Each power domain must be assigned specific cells, and the placement of these cells must take into account factors like routing congestion and orientation.

- 😀 Power gating switches, such as header and footer switches, are used to lower leakage by turning off blocks of the design when they are not in use.

- 😀 Voltage level shifters are required to handle the differences in voltage between domains, such as between 0.7V and 0.9V domains, and between 0.9V and 1.08V.

- 😀 A key challenge in multi-voltage domains is handling both upshifts and downshifts in voltage and ensuring proper data transfer between domains.

- 😀 Special logic gates like DV DC VSL buffers are used to ensure proper voltage conversion when driving signals between domains with different voltage levels.

- 😀 The placement of these voltage level shifters in standard cell rows is complex, and tools must ensure proper routing for secondary power sources.

- 😀 Power gating can be done by placing switches around the power domains in the layout, but interleaving them within the domains themselves offers better power efficiency at the cost of more complex floor planning.

- 😀 Power domain designs require careful consideration of IR drop and resistance in the paths that carry power to the cells, especially when using power gating.

- 😀 Two command formats commonly used in multi-voltage domain design are CPF (Common Power Format) and UPF (Unified Power Format), with UPF being more standardized and widely adopted.

Q & A

What are power domains, and why are they important in low-power design?

-Power domains are regions of a chip that operate at different voltage levels. They are important because they help optimize power consumption by allowing different sections of the chip to operate at the voltage level best suited for their function, thus reducing overall energy usage.

How do you assign cells to different power domains?

-Cells are assigned to power domains by associating them with a specific voltage. For example, RAM may be placed in a 0.7V domain, ROM in a 0.9V domain, and other IP blocks in more complex domains that can switch between different voltages. The placement needs to be physically appropriate to avoid routing issues.

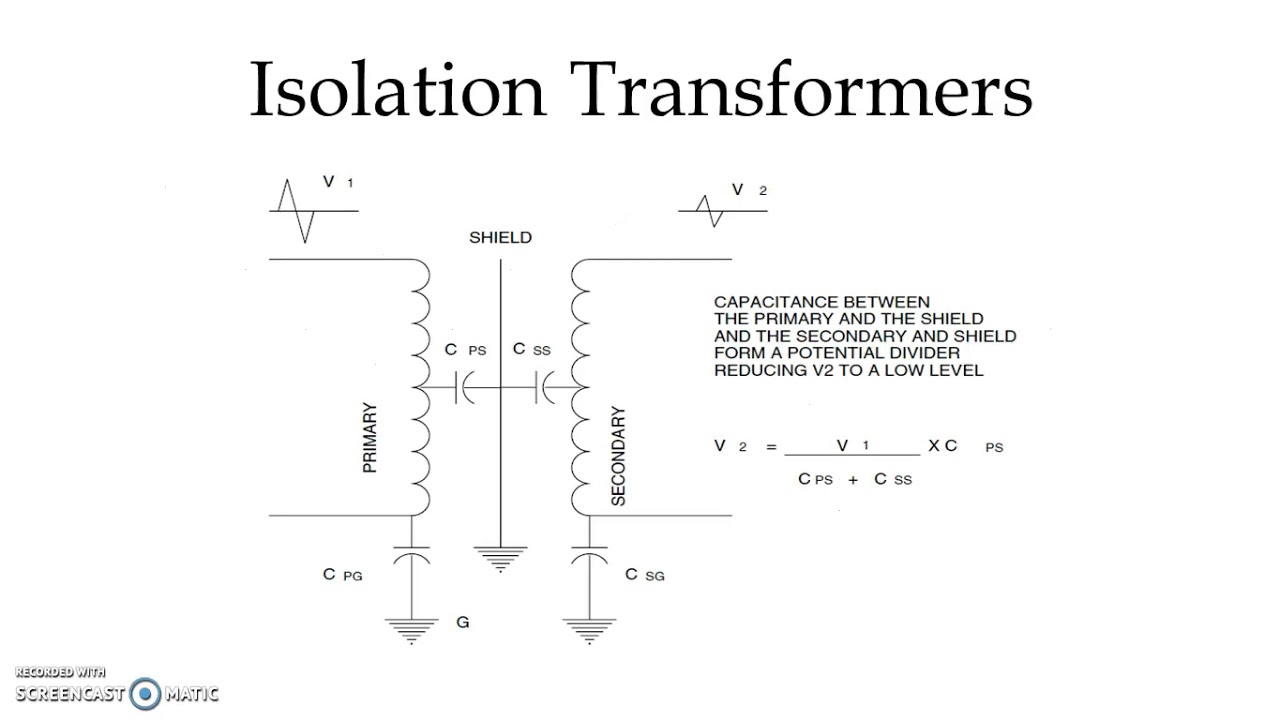

What is the role of level shifters in multiple voltage domain designs?

-Level shifters are used to transfer data between domains operating at different voltages. They ensure that signals are correctly adjusted when transitioning between voltage levels, which could either be an upshift (e.g., 0.7V to 0.9V) or a downshift (e.g., 0.9V to 0.7V).

What are the challenges associated with using level shifters in voltage domain transitions?

-The main challenge is ensuring that level shifters can handle both upshifts and downshifts in voltage reliably. When moving from a lower voltage to a higher voltage, special buffers are required to ensure that the voltage is properly driven. These circuits need to be carefully designed to avoid performance degradation.

What are the two types of switches used in power gating, and how do they work?

-The two types of switches used in power gating are header and footer switches. A header switch is placed between the power supply and the domain, while a footer switch is placed between the domain and ground. These switches are used to disconnect unused blocks to reduce leakage current.

What factors influence the size of power gating switches?

-The size of power gating switches must be large enough to avoid introducing resistance into the path, which could degrade the performance of the chip. The switch size ensures that the domain's power supply is effectively disconnected without affecting the normal operation of the active regions.

What is the difference between header and footer power gating switches?

-A header switch is positioned between the power supply (VDD) and the power domain, whereas a footer switch is placed between the power domain and ground. The difference lies in where they interrupt the current flow to control leakage—header switches control the power supply, and footer switches control the path to ground.

Why is floor planning crucial in managing multiple voltage domains?

-Floor planning is essential for managing the placement of power domains and their associated switches. It ensures that cells are placed within the appropriate voltage domain, that routing congestion is minimized, and that power gating switches are correctly positioned for efficient operation.

What are CPF and UPF, and how do they relate to power domain design?

-CPF (Common Power Format) and UPF (Unified Power Format) are command formats used for managing power in chip design. CPF is used by Cadence tools, while UPF is a standard adopted by Synopsys. Both formats help define the power domains, power gating, and level shifter behavior in the design flow.

How does power gating help in reducing leakage current?

-Power gating reduces leakage current by disconnecting unused blocks or domains from the power supply. By cutting off the power to inactive sections of the chip, power gating minimizes unnecessary power consumption, especially in situations where certain parts of the chip are not needed for operation.

Outlines

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードMindmap

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードKeywords

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードHighlights

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードTranscripts

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレード関連動画をさらに表示

What is VLSI | Introduction & Design flow | VLSI | Lec-01

Low Voltage Switchgear : A Beginner’s Guide | TheElectricalGuy

DC Resistors & Batteries: Crash Course Physics #29

Cures for Low Frequency Disturbances |Power Quality & Management|

Inductors: making high voltage from low voltage

Digital Electronics Ders 1 | MOSFET’e Giriş (İngilizce Terminoloji, Türkçe Anlatım)

5.0 / 5 (0 votes)