Topic 3 in PD: Synthesis Flow Overview: Optimizing RTL to Netlist

Summary

TLDRIn this video, Rashid provides an in-depth overview of the gate-level synthesis process in physical design. Drawing from his 23 years of experience, including 19 years at Intel, he explains the key steps involved, from inputting RTL (Register Transfer Logic) to generating an optimized netlist. The video covers synthesis tools, timing, area, and power optimizations, and highlights the role of constraints and standard cell libraries in determining design efficiency. Rashid also emphasizes the importance of understanding the synthesis flow and reviewing errors and warnings to improve design quality.

Takeaways

- 😀 Gate-level synthesis is the first step in physical design, where RTL code is converted into a netlist consisting of standard cells like gates.

- 😀 Synthesis tools, such as Synopsys Design Compiler and Cadence Genus, not only convert RTL into netlists but also perform optimizations for timing, area, and power.

- 😀 Correct constraints, such as timing, area, power, and floor plan, are essential for generating high-quality synthesis results.

- 😀 The netlist generated by synthesis tools is a text file representing the circuit, containing instances of standard cells (AND, OR, XOR gates, etc.).

- 😀 Optimization of the design is based on critical paths, where tools may select gates with higher drive strength to improve timing while considering area and power consumption.

- 😀 Synthesis tools can choose from different versions of the same gate, varying in drive strength, area, and power, depending on the design's needs.

- 😀 The synthesis flow involves iterations, and reviewing logs and warnings is critical for ensuring optimal design quality.

- 😀 The concept of 'Garbage In, Garbage Out' highlights the importance of inputting correct RTL code, constraints, and libraries to achieve a good output from synthesis tools.

- 😀 Tools like Fusion Compiler integrate synthesis, floor planning, and other tasks into a unified process, offering potential advantages in design flow efficiency.

- 😀 Industry-standard synthesis tools, such as Synopsys and Cadence, automate the conversion of RTL to gate-level designs, ensuring optimization based on user-defined constraints.

- 😀 The synthesis process requires frequent iteration and refinement to ensure the design meets the desired goals for timing, area, and power, with multiple tool commands available for debugging and analysis.

Q & A

What is the main focus of this video?

-The video focuses on providing a high-level overview of gate-level synthesis in physical design, explaining its role in the physical design implementation stage, including the inputs, outputs, and tools involved in the synthesis process.

What is RTL and how does it relate to gate-level synthesis?

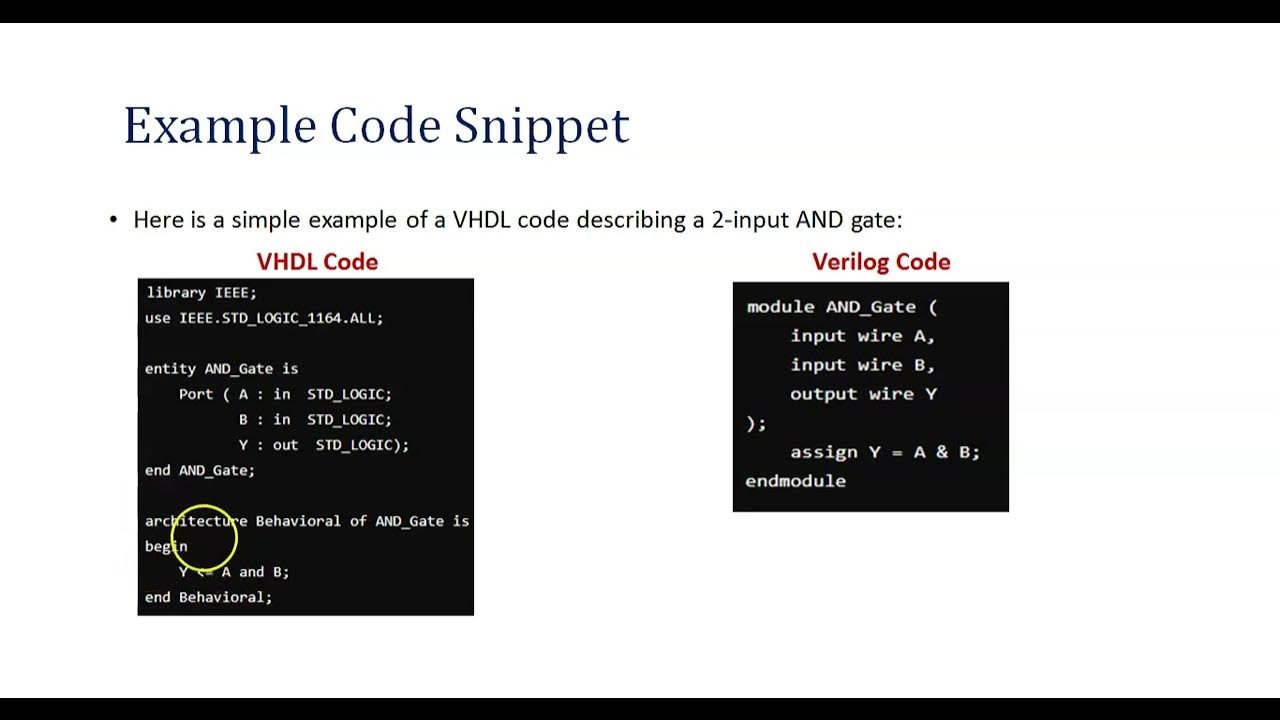

-RTL stands for Register Transfer Logic. It is the input given to the synthesis tool, which converts it into a netlist. The netlist contains the gate-level representation of the design, created from the RTL description.

What is a netlist and what role does it play in synthesis?

-A netlist is a text representation of the circuit, created by the synthesis tool after converting the RTL. It consists of standard cells, temporary wires, and instances of gates, which represent the design in terms of logical gates and their interconnections.

How does synthesis optimize a design beyond simply converting it into a netlist?

-Synthesis not only converts the design into a netlist but also optimizes it for timing, area, and power. The tool evaluates different gate implementations and chooses the most efficient version based on design constraints like area, timing, and power consumption.

What is the significance of standard cells in the synthesis process?

-Standard cells are pre-defined gates or components in a cell library that are used during synthesis. The synthesis tool instantiates these cells in the netlist. Standard cells vary in attributes like drive strength, area, and power consumption, which the tool uses to optimize the design.

How does the synthesis tool select the appropriate gate for the design?

-The synthesis tool selects gates based on constraints such as timing, area, and power. It may choose a gate with a higher drive strength for critical paths to improve timing, while selecting smaller gates for less critical parts to reduce area and power consumption.

What are drive strength and how do they affect the synthesis process?

-Drive strength refers to the ability of a gate to drive current, which is determined by the width of the transistor in the gate. Increasing the drive strength can improve the gate's speed but may increase area and power consumption. The synthesis tool optimizes drive strength based on the criticality of paths in the design.

What role do constraints play in the synthesis process?

-Constraints are crucial for guiding the synthesis tool in optimizing the design. They define timing, area, power, and other factors such as floor planning and voltage levels. The tool uses these constraints to make decisions about gate selection and optimization.

What tools are commonly used in the industry for gate-level synthesis?

-The most widely used tools for gate-level synthesis are Synopsys Design Compiler and Cadence Genus. Additionally, Fusion Compiler by Synopsys offers a unified platform that handles synthesis, floorplanning, and other aspects of physical design.

How important is it to have correct constraints and libraries in synthesis?

-Correct constraints and libraries are essential for achieving a successful synthesis outcome. Incorrect or poorly defined constraints can lead to poor performance, incorrect optimization, or synthesis failures. Ensuring that the right libraries and constraints are used is critical for getting a quality netlist and optimized design.

Outlines

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードMindmap

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードKeywords

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードHighlights

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレードTranscripts

このセクションは有料ユーザー限定です。 アクセスするには、アップグレードをお願いします。

今すぐアップグレード関連動画をさらに表示

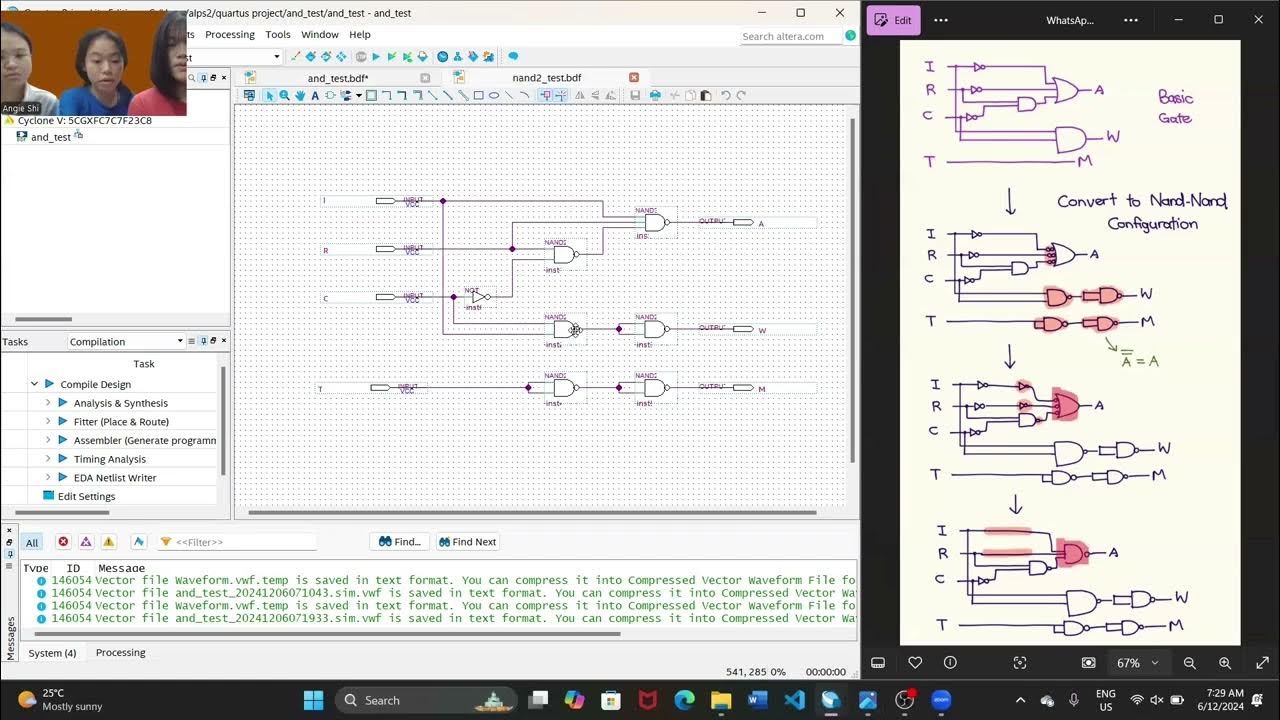

Demonstration of combinational logic design using Quartus Prime software

PD Lec 8 - Netlists | PD Inputs part-2 | VLSI | Physical Design

Introduction to HDL (Hardware Description Language)

CH01_VID04_DBMS Architecture , Data Models

What is VLSI | Introduction & Design flow | VLSI | Lec-01

Dna Replication Part 2

5.0 / 5 (0 votes)