Page Tables and MMU: How Virtual Memory Actually Works Behind the Scenes (Animation)

Summary

TLDRThis video explains the inner workings of virtual memory and how the operating system uses page tables and the Memory Management Unit (MMU) to map virtual addresses to physical ones. It covers key concepts like page table entries, TLBs, and the role of protection bits and status flags. The video also explores the memory management process, including how address translation happens, what happens during a page fault, and how TLB replacement policies optimize memory access. It provides a deep dive into the hardware and software working together to manage memory efficiently.

Takeaways

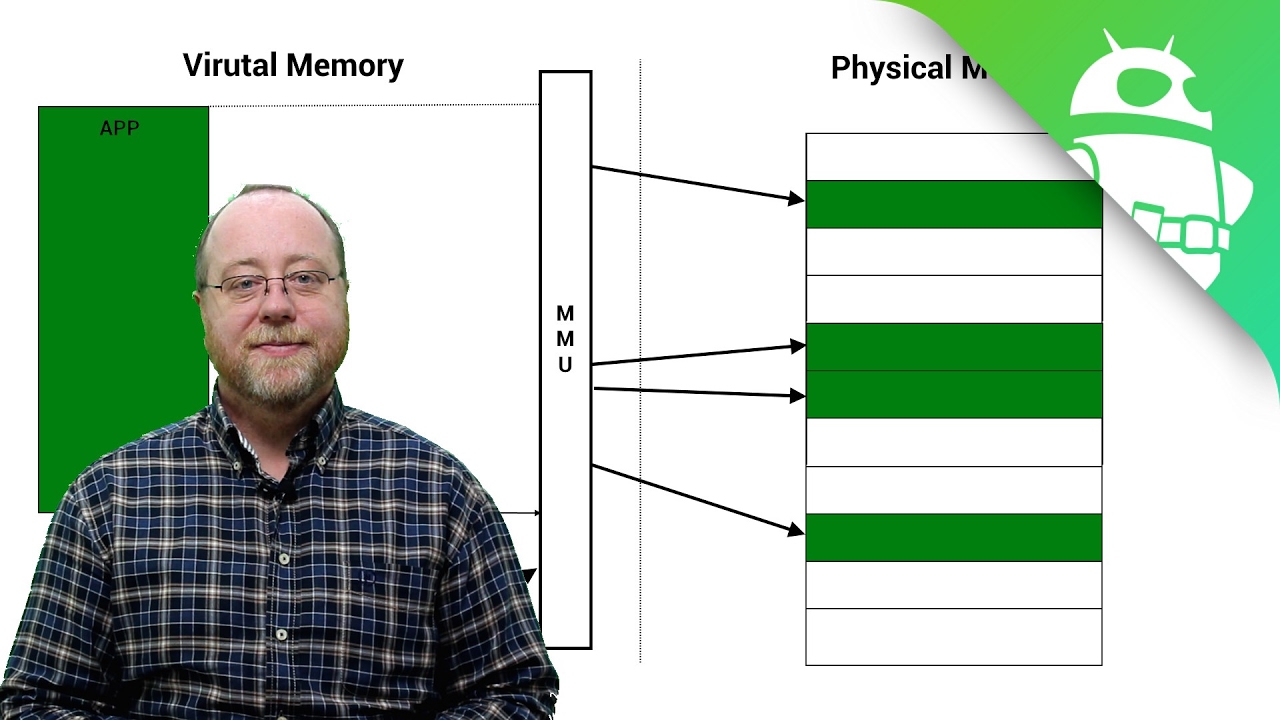

- 🧠 Virtual memory uses pages mapped to physical memory frames, managed via page tables maintained by the operating system.

- 📊 Each process has its own page table, which can become very large, sometimes requiring hundreds of megabytes of memory just for address translation.

- 🔢 Page table entries store the physical frame number, permission bits, and status bits like present, dirty, accessed, and global.

- 🛡️ Protection bits, such as read-only, user/supervisor, and no-execute, prevent unauthorized access and enhance security.

- ⚡ Context switches update the active page table using a page table base register in the CPU.

- 💾 Accessing main memory for every virtual-to-physical translation is slow, so modern CPUs use the Memory Management Unit (MMU) to optimize this process.

- 🧩 The MMU translates virtual addresses into physical addresses and enforces memory access permissions, preventing malicious or erroneous access.

- 🏃 The Translation Lookaside Buffer (TLB) caches recently used page table entries to accelerate address translation and reduce memory access delays.

- 🔄 TLB entries include an Address Space Identifier (ASID) to allow multiple processes' entries to coexist without flushing the TLB on context switches.

- 📉 On a TLB miss, the MMU accesses the full page table, checks validity, and may trigger a page fault if the page is not present or invalid.

- 🗂️ Page faults prompt the OS to allocate free frames, load data from disk, update the page table, and refresh the TLB for future accesses.

- ♻️ TLB replacement policies, like Least Recently Used (LRU), round-robin, or random, determine which entries to evict when the TLB is full.

Q & A

What is the purpose of virtual memory in an operating system?

-Virtual memory allows each process to believe it has its own private memory space, even though the system only has a single physical memory (RAM). It helps in running larger programs by swapping data between RAM and disk storage.

What is a page table, and how does it relate to virtual memory?

-A page table is a data structure used by the operating system to map virtual pages to physical memory frames. Each entry in the page table contains the physical address of the corresponding page in RAM and additional control information such as access permissions.

Why is accessing the page table during each memory access inefficient?

-Accessing the page table for every memory read or write results in two memory accesses: one to fetch the page table entry and another to access the actual data in RAM. This doubles the memory access time, which is slow compared to processor speed.

How does the Memory Management Unit (MMU) help improve memory access efficiency?

-The MMU translates virtual addresses generated by the processor into physical addresses. It uses a cache called the Translation Lookaside Buffer (TLB) to store recently used address translations, reducing the need to access the slower page table in memory.

What is the Translation Lookaside Buffer (TLB) and how does it function?

-The TLB is a small, fast cache in the MMU that stores recently accessed page table entries. It speeds up the address translation process by providing a quick lookup for virtual to physical address mappings, reducing memory access time.

What happens when a virtual address is not found in the TLB?

-When a virtual address is not found in the TLB (a TLB miss), the MMU must access the full page table in memory to obtain the correct translation. This process takes longer and is less efficient.

What is a page fault and how does the operating system handle it?

-A page fault occurs when a process tries to access a page that is not currently loaded in physical memory. The operating system handles the page fault by loading the required page from disk into memory and updating the page table and TLB accordingly.

Why are page table entries so large in modern systems?

-Page table entries can be large because they must store a variety of information, including the physical frame number, protection bits, and status flags for each page. In large memory systems, the number of entries in a page table can grow significantly.

What is the role of the protection and permission bits in page table entries?

-The protection bits control whether a page can be read, written to, or executed. These bits are used to enforce security and prevent unauthorized access, such as stopping user-level processes from modifying critical operating system data.

How does the MMU prevent different processes from accessing each other's memory?

-The MMU uses the **Address Space Identifier (ASID)**, which links each TLB entry to a specific process. This ensures that processes cannot access memory that belongs to another process, providing isolation and security between them.

Outlines

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenMindmap

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenKeywords

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenHighlights

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenTranscripts

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenWeitere ähnliche Videos ansehen

What is virtual memory? – Gary explains

But, what is Virtual Memory?

Paging in Operating Systems with Example & Working - Memory Management

Sistemas Computacionais - Técnica de memória virtual: paginação e segmentação

L-5.9: What is Paging | Memory management | Operating System

CISY 217 Virtual Memory - Demand Paging

5.0 / 5 (0 votes)