C09P01 - Translation Lookaside Buffer TLB - ISI485 - Sistemas Operativos

Summary

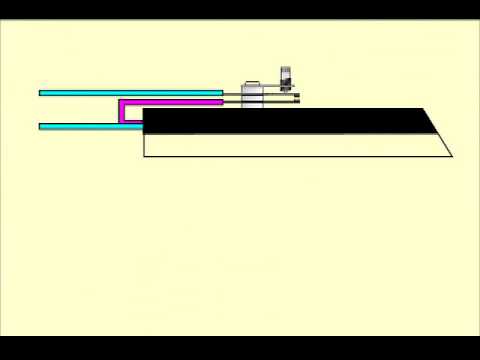

TLDREl video explica el funcionamiento del acceso a memoria en programas, enfocándose en el principio de localidad espacial y temporal. Se analiza cómo el uso de una memoria caché, como el Translation Lookaside Buffer (TLB), mejora el rendimiento al reducir los accesos a la memoria física. El TLB acelera la traducción de direcciones lógicas a físicas, manteniendo las traducciones más utilizadas cerca de la CPU. Si no se encuentra una dirección en el TLB, se accede a la tabla de páginas en memoria, actualizando el TLB para mejorar futuras referencias, optimizando así el desempeño del sistema.

Takeaways

- 🖥️ El programa descrito accede a un arreglo de mil posiciones y actualiza la memoria en cada iteración de su ciclo.

- 🔄 El ciclo de actualización de memoria implica cuatro instrucciones en lenguaje ensamblador x86.

- 🔗 Los principios de localidad temporal y espacial son fundamentales para el acceso a memoria eficiente, ya que las instrucciones y datos adyacentes son reutilizados.

- 🚀 La memoria caché optimiza el acceso a datos y a las instrucciones mediante el almacenamiento de bloques de datos cercanos, lo que acelera el proceso.

- 📑 La paginación añade complejidad, ya que se requieren accesos adicionales a la tabla de páginas para conocer las direcciones físicas de los datos y las instrucciones.

- ⚙️ El TLB (Translation Lookaside Buffer) es una memoria caché especializada en acelerar la traducción de direcciones lógicas a físicas, evitando accesos constantes a la tabla de páginas.

- ⏳ El TLB mejora el rendimiento al almacenar traducciones de direcciones que son utilizadas con mayor frecuencia cerca de la CPU.

- 🧠 En caso de un TLB miss, se accede a la tabla de páginas en la memoria física para obtener la traducción necesaria, lo que penaliza el rendimiento.

- 📊 La capacidad de mantener las traducciones populares en el TLB optimiza significativamente el desempeño del sistema de memoria virtual.

- 💡 La integración del TLB en el hardware de la CPU permite mejorar el rendimiento general del sistema al minimizar los accesos a la memoria física.

Q & A

¿Qué es el TLB (Translation Lookaside Buffer) en el contexto de la memoria?

-El TLB es una memoria caché de hardware diseñada para acelerar el proceso de traducción de direcciones lógicas a direcciones físicas, almacenando las traducciones más utilizadas cerca de la CPU para mejorar el rendimiento.

¿Cuál es el propósito principal del TLB en un sistema de memoria virtual?

-El propósito principal del TLB es reducir el número de accesos a la tabla de páginas y la memoria física, mejorando así el rendimiento del sistema al hacer que las traducciones de direcciones sean más rápidas.

¿Qué es el 'principio de localidad temporal' en el acceso a la memoria?

-El principio de localidad temporal indica que si una instrucción o dato es accedido en un momento dado, es probable que sea necesario nuevamente en un futuro cercano, optimizando el uso de la caché.

¿Qué es el 'principio de localidad espacial' y cómo se relaciona con la caché?

-El principio de localidad espacial sostiene que si se accede a una dirección de memoria, es probable que las direcciones cercanas también sean accedidas pronto. Esto permite que se carguen varias direcciones adyacentes en la caché para mejorar el rendimiento.

¿Qué diferencia hay entre un 'TLB hit' y un 'TLB miss'?

-Un 'TLB hit' ocurre cuando la traducción de una dirección lógica a física se encuentra en el TLB, permitiendo un acceso rápido. Un 'TLB miss' ocurre cuando no se encuentra la traducción, lo que obliga a acceder a la tabla de páginas en memoria, ralentizando el proceso.

¿Cómo afecta la paginación al rendimiento del acceso a la memoria?

-La paginación introduce accesos adicionales a la tabla de páginas, lo que puede ralentizar el sistema. Sin embargo, el uso del TLB minimiza este impacto al almacenar las traducciones más frecuentes en una memoria caché cercana a la CPU.

¿Cómo se organiza la memoria de un programa típico en el contexto de este video?

-Un programa típico está organizado con instrucciones almacenadas en la región de código y datos, como arreglos, en áreas específicas de la memoria. Los accesos a estas áreas se optimizan mediante cachés y tablas de páginas.

¿Por qué se dice que el TLB es una caché de traducción de direcciones?

-El TLB se considera una caché de traducción de direcciones porque almacena en hardware las traducciones más frecuentemente utilizadas, evitando así accesos continuos a la tabla de páginas en memoria.

¿Cómo se puede mejorar el rendimiento del sistema de memoria utilizando un TLB?

-El rendimiento mejora manteniendo en el TLB las traducciones de direcciones más utilizadas, lo que reduce la necesidad de acceder constantemente a la memoria física para la traducción de direcciones.

¿Qué pasa si una dirección lógica no se encuentra en el TLB?

-Si una dirección lógica no se encuentra en el TLB, se genera un 'TLB miss' y se accede a la tabla de páginas en la memoria física para obtener la traducción, lo que actualiza el TLB para futuros accesos.

Outlines

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenMindmap

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenKeywords

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenHighlights

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenTranscripts

Dieser Bereich ist nur für Premium-Benutzer verfügbar. Bitte führen Sie ein Upgrade durch, um auf diesen Abschnitt zuzugreifen.

Upgrade durchführenWeitere ähnliche Videos ansehen

Funcionamiento cognitivo y emocional: Cómo el cerebro procesa la cognición y las emociones.

Tutorial C++ 22. Punteros

La memoria principal del ordenador: RAM, ROM y caché

¡Todo, TODO sobre la RAM! - Parte 1 | Nate Labs

Neuropsicología: Memoria de Trabajo- Funciones Ejecutivas

Como funciona una plancha para ropa

5.0 / 5 (0 votes)