#18 interrupts Part-3: How interrupts work on ARM Cortex-M?

Summary

TLDRIn this lesson, Miro Samek dives into how ARM Cortex-M handles interrupts and why interrupt handlers can be regular C functions. Through an experimental approach, the video demonstrates how the Cortex-M saves registers and handles interrupt returns. The lesson explains ARM’s efficient method of managing interrupts with minimal stack usage, including the use of special return values in the LR register. The impact of the Floating Point Unit (FPU) on interrupt stack frames is also discussed, highlighting how it increases stack size and affects performance. The lesson concludes by preparing viewers for future topics on race conditions and real-time operating systems.

Takeaways

- 😀 ARM Cortex-M allows interrupts to be handled by regular C functions, making the interrupt handling process more flexible compared to other CPUs.

- 😀 The ARM Cortex-M solution for interrupt handling is based on saving and restoring CPU registers using a standard stack frame, complementing the ARM Procedure Call Standard (AAPCS).

- 😀 Unlike MSP430, which uses special instructions for interrupts, ARM Cortex-M uses data in the Link Register (LR) to handle returns from interrupts, making the process more versatile.

- 😀 SysTick interrupts can be manually triggered using the Interrupt Control and State Register (ICSR), specifically setting bit 26 to create a pending interrupt state.

- 😀 ARM Cortex-M manages interrupt processing efficiently with only 12 clock cycles needed to push or pop 8 registers to/from the stack.

- 😀 Stack misalignment in ARM Cortex-M is handled using an optional 'aligner' word to ensure the stack is aligned to 8-byte boundaries, enhancing processing speed and preventing errors.

- 😀 When the Floating Point Unit (FPU) is enabled, the interrupt stack frame increases significantly, requiring more stack space and longer entry/exit times for interrupts.

- 😀 The Cortex-M interrupt stack frame is designed to be compatible with the ARM Procedure Call Standard (AAPCS), which ensures consistency across different compilers.

- 😀 The standard return from an interrupt on ARM Cortex-M uses a special value in the LR register to signal the return to the interrupted point in the program.

- 😀 The impact of FPU usage on interrupt handling highlights the importance of stack size considerations and performance trade-offs when working with floating-point operations.

Q & A

How does ARM Cortex-M handle interrupts compared to MSP430?

-ARM Cortex-M uses regular C functions as interrupt handlers, unlike MSP430 which requires special instructions (RETI) for interrupts. Cortex-M uses the LR register with a special value to return from interrupts, making the process more flexible and similar to regular function calls.

What is the significance of the LR register in ARM Cortex-M interrupt handling?

-The LR register in ARM Cortex-M is loaded with a special value (e.g., 0xFFFFFFF9) during an interrupt, signaling that the return is from an interrupt. This eliminates the need for special instructions like RETI, which are used in other CPUs like MSP430.

How can you trigger a SysTick interrupt manually in ARM Cortex-M?

-In ARM Cortex-M, you can trigger the SysTick interrupt by setting the PENDSTSET bit in the Interrupt Control and State Register (ICSR), bypassing the usual method of writing to the STCURRENT register.

What is the purpose of the 'aligner' word in the interrupt stack frame?

-The 'aligner' word is used to ensure the stack is aligned to an 8-byte boundary. This alignment is necessary for optimized register transfers, and it prevents misalignment during interrupt handling, which could affect performance.

What is the effect of enabling the Floating Point Unit (FPU) on interrupt handling in ARM Cortex-M?

-When the FPU is enabled, the interrupt stack frame becomes significantly larger, as it must accommodate floating-point registers. Additionally, interrupt entry and exit times are longer due to the increased complexity of handling floating-point operations.

What are the two main processor states in ARM Cortex-M during exception handling?

-The two main processor states in ARM Cortex-M are 'Handler mode,' which occurs when the processor handles an interrupt or exception, and 'Thread mode,' which is used for regular program execution, such as running the main program loop.

What is the role of the ARM Application Procedure Call Standard (AAPCS) in interrupt handling?

-The AAPCS defines which registers must be preserved during function calls, including interrupt handlers. ARM Cortex-M interrupt handling aligns with this standard, ensuring that registers are saved and restored in a consistent manner, making interrupt handlers regular C functions.

How does ARM Cortex-M achieve interrupt return without a special instruction like RETI?

-ARM Cortex-M achieves interrupt return using the standard BX LR instruction. The LR register holds a special value (e.g., 0xFFFFFFF9) upon interrupt entry, and when the BX LR instruction is executed, it causes the processor to return from the interrupt using the contents of LR.

Why is stack alignment important in ARM Cortex-M interrupt handling?

-Stack alignment is important because ARM Cortex-M requires the stack to be aligned to 8-byte boundaries for optimized performance. Misalignment could slow down the processor and cause inefficiencies in handling interrupt stack frames.

What happens if the stack is misaligned during interrupt handling on ARM Cortex-M?

-If the stack is misaligned during interrupt handling, the 'aligner' word is added to the stack frame to ensure proper alignment. This alignment ensures that the registers are transferred efficiently and the interrupt can be handled correctly.

Outlines

此内容仅限付费用户访问。 请升级后访问。

立即升级Mindmap

此内容仅限付费用户访问。 请升级后访问。

立即升级Keywords

此内容仅限付费用户访问。 请升级后访问。

立即升级Highlights

此内容仅限付费用户访问。 请升级后访问。

立即升级Transcripts

此内容仅限付费用户访问。 请升级后访问。

立即升级浏览更多相关视频

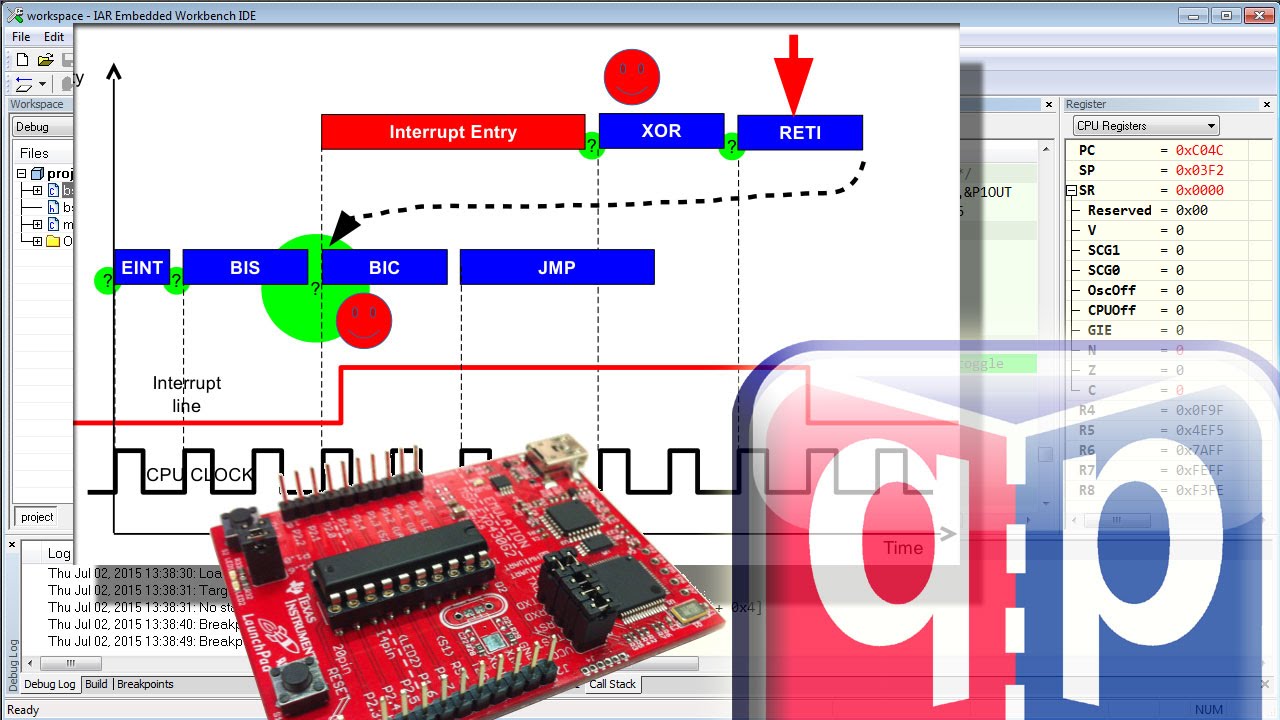

#17 interrupts Part-2: How most CPUs (e.g. MSP430) handle interrupts?

#8 Functions in C and the call stack

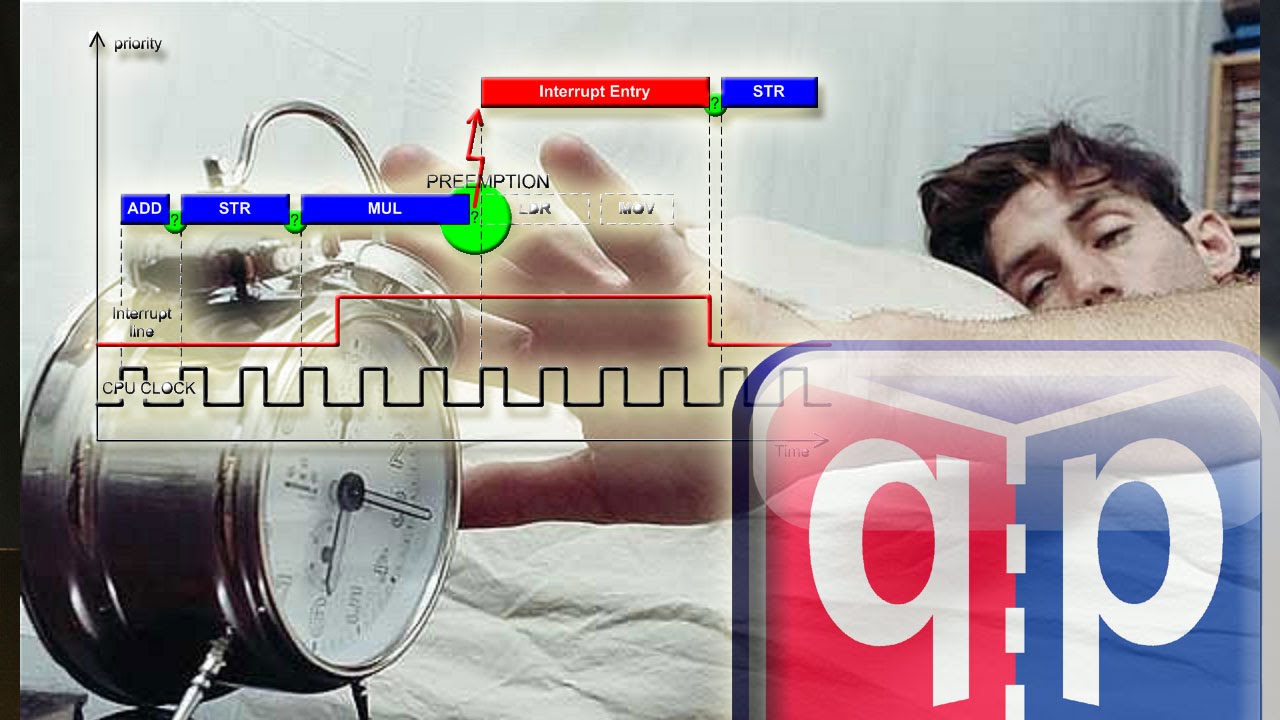

#16 Interrupts Part-1: What are interrupts, and how they work

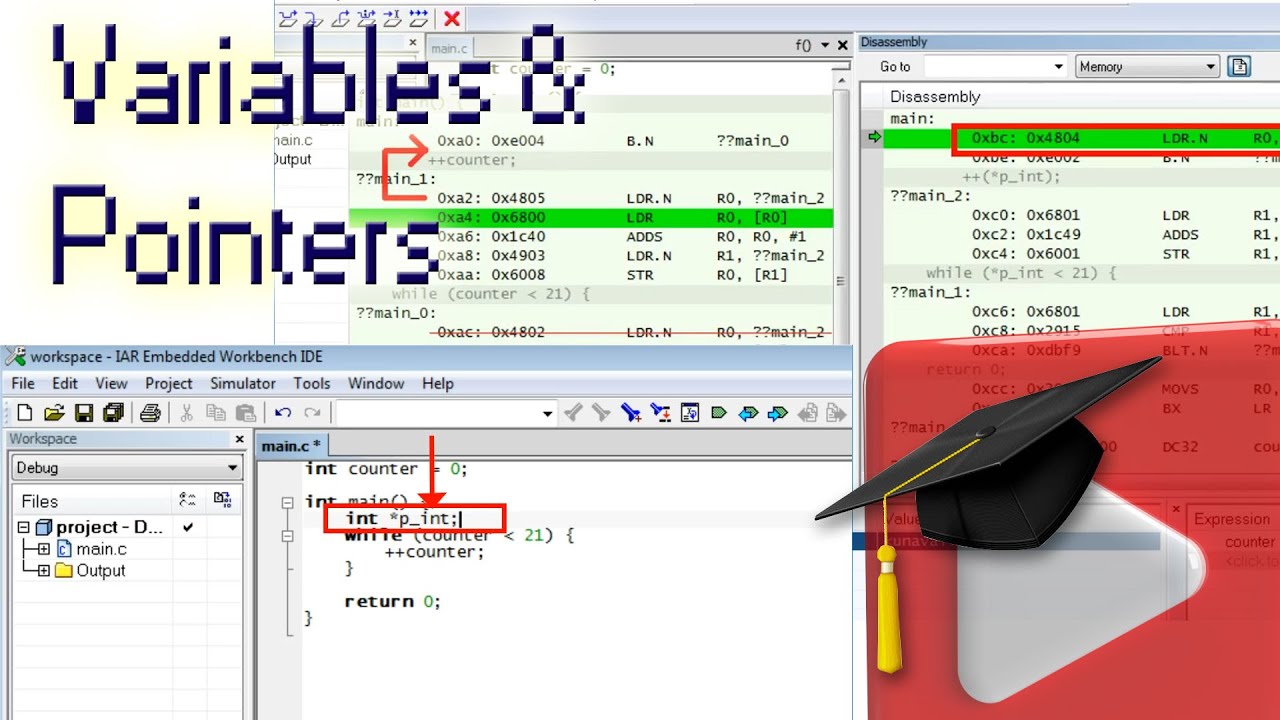

#3 Variables and Pointers

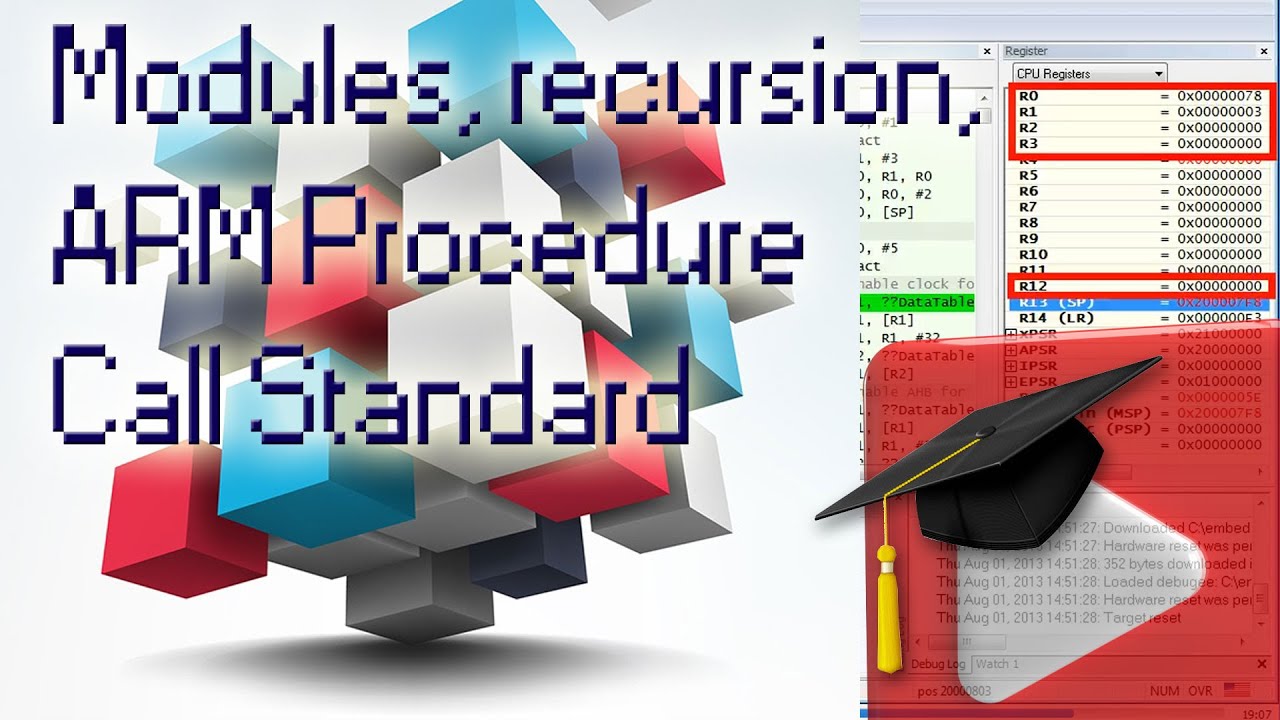

#9 Modules, Recursion, ARM Application Procedure Call Standard (AAPCS)

#13 Startup Code Part-1: What is startup code and how the CPU gets from reset to main?

5.0 / 5 (0 votes)